Technische Universität München Department of Electrical Engineering and Information Technology Institute for Electronic Design Automation

# Structure and Signal Path Analysis for Analog and Digital Circuits

Michael Eick

Vollständiger Abdruck der von der Fakultät für Elektro- und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

**Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzende: Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

Prüfer der Dissertation: 1. Priv.-Doz. Dr.-Ing. Helmut Gräb

2. Univ.-Prof. Dr.-Ing. habil. Lars Hedrich Johann Wolfgang Goethe Universität, Frankfurt am Main

Die Dissertation wurde am 17. Januar 2013 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektro- und Informationstechnik am 8. Mai 2013 angenommen.

#### **Abstract**

This thesis presents a new method for the automatic structural analysis of analog and digital integrated circuits. The method provides automatic recognition of basic analog and digital building blocks, automatic identification of analog and digital signal paths as well as symmetry computation. Applications in the context of automatic analysis of digital standard cells as well as automatic sizing and placement of analog circuits are presented.

## Kurzfassung

Diese Arbeit stellt eine neue Methode zur automatische Strukturanalyse von analogen und digitalen integrierten Schaltungen vor. Sie umfasst eine automatische Erkennung analoger und digitaler Grundblöcke, eine automatische Bestimmung analoger und digitaler Signalpfade sowie die Berechnung von Symmetrien. Die Arbeit stellt Anwendungen im Bereich der automatischen Analyse von digitalen Standardzellen sowie der automatischen Dimensionierung und Platzierung analoger Schaltungen vor.

## **Preface**

This thesis summarizes my research work at the Institute for Electronic Design Automation. Therefore, I would like to thank the head of this institute, Prof. Dr.–Ing. Ulf Schlichtmann, for giving me this opportunity. A special thanks to PD Dr.–Ing. Helmut Graeb for being my advisor and all the fruitful discussions. These discussion were of great importance for quality and extend of this thesis and the related publications. I also would like to thank Prof. Dr.–Ing. Lars Hedrich for his work as second examiner and his attention to my work. Furthermore, I thank Prof. Dr. Doris Schmitt–Landsiedel for taking the chair of my committee and Prof. Dr.–Ing. Maurits Ortmanns for being my mentor in the TUM Graduate School.

Special thanks go to all my former colleagues at the institute and the members of the so-called analog group in particular. I will never forget the cooperativeness and great atmosphere. Especially, I would like to thank Dr.-Ing. Martin Strasser for his great support of my experiments on placement constraints. I would like to thank Gertraude Kallweit, Susanne Werner, Werner Tolle and Hans Ranke for keeping the institute running. I was able to find some great students who were willing to explore my ideas, whom I would like to thank at this point.

Furthermore, I would like to thank the people from the Infineon Technologies AG for their support, especially Jens Bargfrede and Bernhard Lippmann. I would like to commemorate Michael Mirbeth, who died in 2009. He gave me great support as well.

Thanks go also to the researchers from the Austin Research Laboratory of IBM for two very interesting weeks in Austin, particularly, Dr. Sani Nassif and Jente Benedict Kuang, PhD.

Without my parents' support I would never have gotten that far. Therefore, I would like to thank them. Finally, a special thanks to thank my friends for the great time outside university.

Munich, June 2013

# Contents

| 1. | Intr | oduction                                                    | 1   |  |  |  |  |

|----|------|-------------------------------------------------------------|-----|--|--|--|--|

|    | 1.1. | Research Needs in Constraint-Driven Design                  | 2   |  |  |  |  |

|    | 1.2. | Structural Analysis for Digital Circuits                    | 4   |  |  |  |  |

|    | 1.3. | Contributions of this Work                                  | 4   |  |  |  |  |

| 2. | Stat | te of the Art                                               | 7   |  |  |  |  |

|    | 2.1. | Structural Analysis for Analog Circuits                     | 7   |  |  |  |  |

|    | 2.2. | Behavioral Analysis                                         | 15  |  |  |  |  |

|    | 2.3. | Constraint Generation for Analog Circuits                   | 17  |  |  |  |  |

|    | 2.4. | Structural Analysis for Digital Circuits                    | 19  |  |  |  |  |

| 3. | Enh  | Enhanced Building Block Analysis                            |     |  |  |  |  |

|    | 3.1. | Library of Analog and Digital Building Blocks               | 21  |  |  |  |  |

|    | 3.2. | Enhanced Algorithm                                          | 28  |  |  |  |  |

|    | 3.3. | Discussion                                                  | 41  |  |  |  |  |

|    | 3.4. | Experimental Results                                        | 47  |  |  |  |  |

| 4. | Stru | ictural Signal Path Analysis                                | 53  |  |  |  |  |

|    | 4.1. | Generation of Enhanced Structural Signal Flow Graphs        | 53  |  |  |  |  |

|    | 4.2. | Automatic Identification of Analog and Digital Part         | 63  |  |  |  |  |

|    | 4.3. | Automatic Identification of Core and Bias Part              | 68  |  |  |  |  |

|    | 4.4. | Pass Gate Direction Assignment                              | 71  |  |  |  |  |

|    | 4.5. | Feedback Analysis                                           | 74  |  |  |  |  |

| 5. | Sym  | nmetry Computation                                          | 79  |  |  |  |  |

|    | 5.1. | Preliminary Considerations                                  | 79  |  |  |  |  |

|    | 5.2. | Symmetry Problem on ESFG Level                              | 84  |  |  |  |  |

|    | 5.3. | Algorithm                                                   | 89  |  |  |  |  |

|    | 5.4. | Experimental Results                                        | 96  |  |  |  |  |

| 6. | Арр  | lication: Input Data Generation for Timing Characterization | 101 |  |  |  |  |

|    | 6.1. | Logic Function Extraction                                   | 101 |  |  |  |  |

|    | 6.2. | Type Detection                                              | 110 |  |  |  |  |

|    | 6.3. | Vector Generation                                           | 110 |  |  |  |  |

|    | 6.4  | Experimental Results                                        | 11( |  |  |  |  |

## Contents

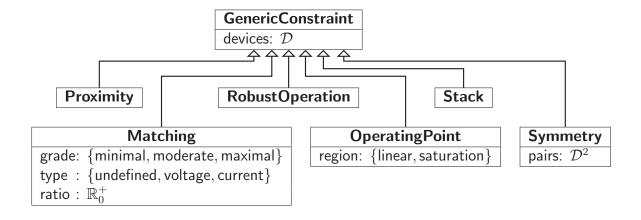

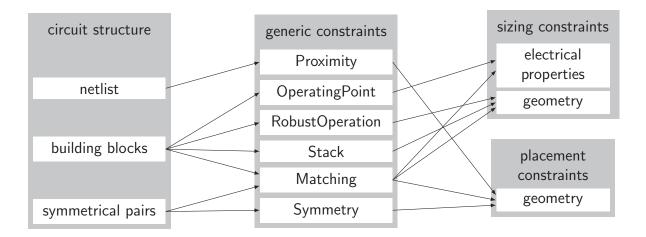

| 7.  | Application: Constraint Generation for Analog Circuits                    | 113 |

|-----|---------------------------------------------------------------------------|-----|

|     | 7.1. Generic Constraints                                                  | 113 |

|     | 7.2. Constraint Generation                                                | 115 |

|     | 7.3. Experimental Results                                                 |     |

| 8.  | Conclusion                                                                | 131 |

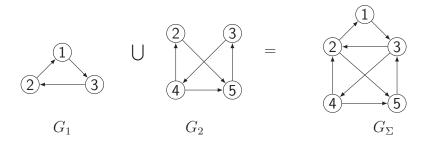

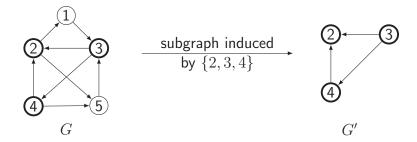

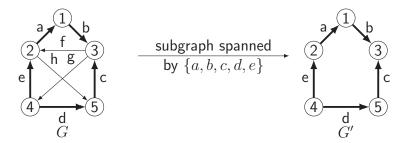

| Α.  | Graph Theoretical Definitions                                             | 133 |

|     | A.1. Graphs and Subgraphs                                                 | 133 |

|     | A.2. Properties of Graphs                                                 | 134 |

|     | A.3. Operations on Graphs                                                 | 134 |

|     | A.4. Isomorphism                                                          | 135 |

| В.  | Equivalence of Conflict Resolution Techniques for Building Block Analysis | 137 |

| Gl  | ossary                                                                    | 147 |

| Bil | bliography                                                                | 151 |

## 1. Introduction

Analog and mixed-signal circuits play an important role in today's electronic systems. The International Technology Roadmap for Semiconductors lists, among others, consumer, communication and automotive applications (ITRS 2011, System Driver Chapter). It defines analog or mixed-signal circuits to be circuits that at least partially deal with input signals whose precise values matter (ITRS 2011, System Driver Chapter, p.16). These circuits are mainly required for analog to digital and digital to analog conversion to read out sensors or control actuators. It lists shortage of design productivity (ITRS 2011, System Driver Chapter, p.25) emerging from poor automation as one of the main challenges for future mixed-signal systems.

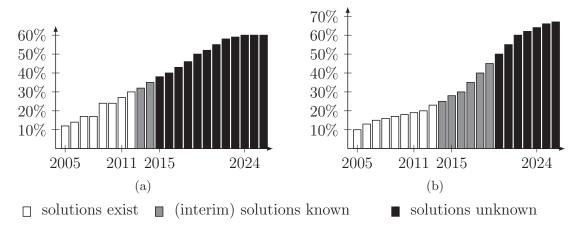

In the design chapter of the same work, more detailed goals are formulated. Figure 1.1a shows the degree of automation required for analog components in comparison to the degree of automation for digital circuits. Figure 1.1b illustrates the amount of circuits that should be synthesized. For the years starting from 2011 data is taken from ITRS (2011, design chapter, Tables DESN2a, DESN2b, DESN4). For years 2005 to 2011 data from ITRS (2005, design chapter, Tables 13a and 15a) is used. Both, ITRS (2005) and ITRS (2011) state that in 2011 analog automation reaches 27% of

Figure 1.1.: Requirements for analog design automation as formulated by the ITRS (ITRS 2005, ITRS 2011). (a) Degree of automation for analog designs in percent of automation for digital designs. (b) Percentage of synthesized analog content.

#### 1. Introduction

digital automation and 19% of synthesized analog content. Therefore, it is assumed that the intermediate goals from 2005 to 2011 were met.

Some amount of this increase might be due to the better integration of constraint—driven design and some basic design automation algorithms in major CAD tools. The idea is that analog and mixed—signal designs are heavily dependent on so—called constraints. Constraints describe all conditions that must be held for an analog circuit to work correctly but are normally not part of the specification. Examples for constraints are matching conditions, operating region conditions (e.g., saturation) or symmetry conditions. An example for a commercial software enabling constraint—driven design is Cadence® Virtuoso® 6 (Cadence Design Systems 2008). It contains a constraint manager to edit and store constraints in the design database. It provides basic methods to generate constraints using automatic recognition of building blocks like simple current mirrors and symmetry analysis. The constraints are then automatically considered in the layout editor. In order to be able to use design automation for sizing (Martens & Gielen 2008) or placement (Graeb 2011) without excessive setup, machine readable storage of constraints is necessary. In this context three problems can arise,

- 1. Traditionally, constraints were rarely documented. Maybe, important constraints were noted in some annotation layer.

- 2. Modern design software allows to store the constraints in machine—readable form with the design. However, entering all constraints for an existing or new design is tedious.

- 3. In the case that the constraints of a design were stored in machine–readable form, completeness becomes an issue. For sizing and placement tools, completeness of the constraints is important. Otherwise, they may find inappropriate solutions which an experienced designer would exclude from the beginning.

Automatic generation of constraints is an approach to tackle all these three problems.

# 1.1. Research Needs in Constraint-Driven Design

For the degree of analog automation, Fig. 1.1 shows a long term goal of 60%. For the amount of synthesized content the long term goal is 67%. However, today's technology, including research results, will limit the degree of automation to 35% which should be reached in 2014. The amount of synthesized content is limited to 45% which should be reached in 2019. Thus, further research in the area of analog design automation is necessary to reach the long term goals.

Further progress is expected trough interactive design aids (ITRS 2011, design chapter). Such an interactive design aid must fulfill two major requirements. First, it

must be well integrated with the overall design environment. Second, the required initial set-up must be low to allow the designer a quick start and refine settings afterward. This is especially true for the constraints, which in turn requires an enhanced constraint-driven design.

Necessary enhancements in constraint—driven design are discussed in the following. According to Jerke et al. (2011) constraint—driven design requires a constraint management system, the possibility to generate or derive constraints from design objectives, the possibility to transform higher level constraints into lower level constraints, constraint verification and constraint sensitivity analysis. Constraint generation or constraint extraction is also identified as key issue by Rutenbar (2012). Enhancement of the state of the art is possible for most components:

## • Constraint Management/Representation

In current constraint management systems, constraints are often stored in a tool—specific way. This applies to the types of constraints provided as well as the parameters available for some specific constraint. This becomes a problem when various tools shall use the same set of constraints. In most systems, additional constraints can be defined by the user. However, a generic constraint set, applicable to different tools and circuits is not yet known.

#### • Constraint Generation

Multiple approaches to automatic constraint generation were discussed in the literature (see Section 2.3). Most algorithms analyze the topology of the circuit for building blocks and/or symmetry. For example, the transistors of a simple current mirror always have to work in saturation region and must be matched. Symmetry is a widely used principle, where a circuit is designed to consist of two identical halves. A typical example are fully-differential circuits. For these circuits, high CMRR and low-offset error can only be obtained if the corresponding symmetry constraints for sizing and layout are completely available and are obeyed. Consequently, circuit symmetry should be computed from behavioral considerations. State-of-the-art algorithms focus on the topology of the circuit and the sizing and cannot handle multiple symmetrical signal paths that cross each other.

#### • Constraint Transformation

Constraint transformation was considered little in research so far. Some work can be found for AC constraint transformation and in the field of hierarchical synthesis (see Section 2.3). The symmetry computation problem mentioned above can also be interpreted as constraint transformation of symmetry constraints on behavioral level to symmetry constraints on transistor level.

## • Constraint Verification

Two different problems occur in the context of constraint verification. On the one hand, the completed design must be checked for constraint violations. On the

#### 1. Introduction

other hand, the constraints must be checked for completeness and contradictions. This problem is closely related to the constraint generation problem. Thus, methods developed for the constraint generation problem will push constraint verification forward as well.

This thesis will present new solution approaches to above problems. In particular, it investigates different approaches for constraint generation for analog circuits using structural analysis. It presents a new symmetry computation that is based on constraint transformation. In addition, a data structure for generic representation of constraints for different applications is presented.

## 1.2. Structural Analysis for Digital Circuits

The use of structural analysis methods is not limited to constraint generation. For digital circuits, structural analysis is a well established method (see Section 2.4). In this work, it will be shown that structural analysis for analog and digital circuits can be performed using the same methods. This is beneficial for circuits containing analog and digital components at the same time. Examples are analog circuits with some digital gates controlling power-down mode or mixed-signal circuits.

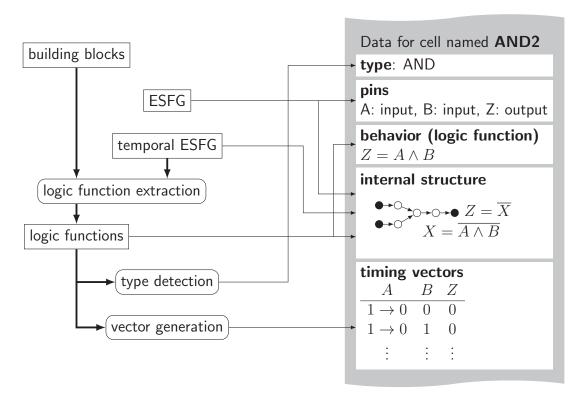

Timing characterization for digital standard cells determines the delay of a cell in dependence of the switching pattern and cell load. To perform this automatically, several input data like the logic function of the cell is required. Information about the internal structure of a cell becomes important for advanced techniques. For example the current–source modeling approach of Knoth et al. (2009) as well as the aging analysis approach of Lorenz et al. (2010) require a decomposition of the standard cell into single stage gates. This thesis will show that the suggested method can generate this information.

### 1.3. Contributions of this Work

The structural analysis method presented in this thesis is suitable but not limited to the applications discussed above. In particular, these are constraint generation for analog circuits and generation of structural and behavioral information for timing characterization of digital standard cells.

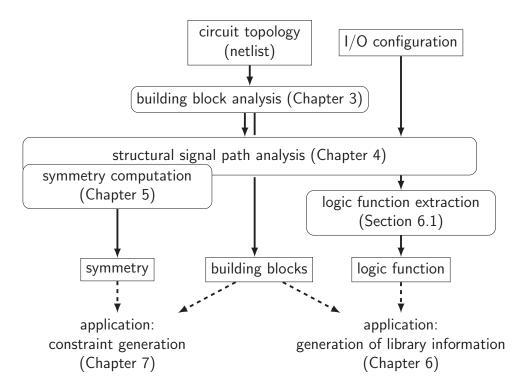

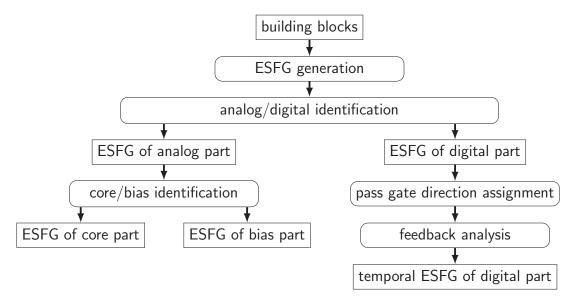

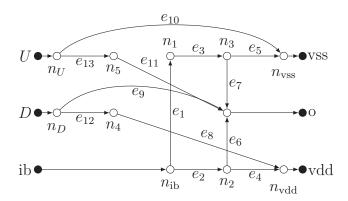

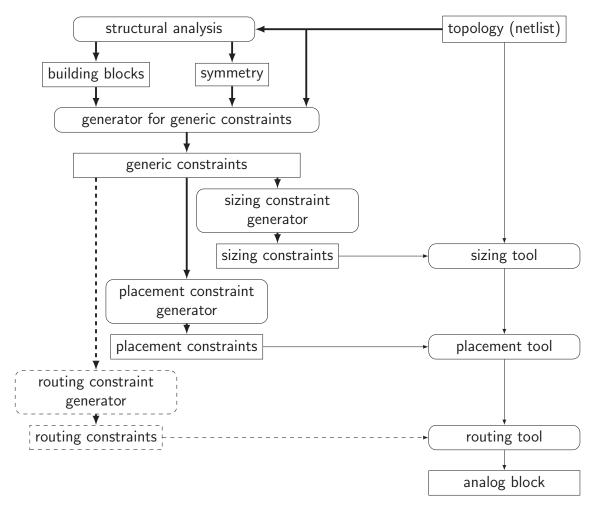

An overview of the proposed method is given in Fig. 1.2. Starting point is the circuit topology which is typically a netlist as well as a description of the inputs and outputs of the circuit. Based on the circuit topology a building block analysis is performed, which recognizes analog building blocks like simple current mirrors or digital building blocks like pass gates. After that, a structural signal path analysis is performed which is based on a structural and qualitative behavioral model of the circuit, the

Figure 1.2.: Overview of the proposed method.

so—called ESFG. The analysis includes an automatic identification of the analog and digital part of a circuit as well as the core and bias part, a computation of true pass gate directions, automatic breaking of feedback loops and a symmetry computation. For digital circuits, the results of the structural signal path analysis are then used to compute the overall logic function of the circuit.

The method includes the following contributions compared to state of the art (see Chapter 2).

## 1. Building Block Analysis

Traditional approaches for building block analysis either focus on analog or digital circuits. This is the first method that can handle analog and digital building blocks simultaneously. In addition, it contains several runtime improvements compared to the basic algorithm (Massier 2010).

#### 2. Structural Signal Path Analysis

The structural signal path analysis is based on a new graph model, the ESFG. It is the first model, that includes the structure of the circuit described by its building blocks as well as its qualitative behavior. This thesis presents the following analyses based on that model:

- a) a method to automatically identify the core and bias part of a circuit,

- b) a method to automatically identify the analog and digital part of a circuit,

#### 1. Introduction

- c) a method to detect the true directions of pass gates within the digital circuit part,

- d) a method to break feedback loops within the digital circuit part.

#### 3. Symmetry Computation

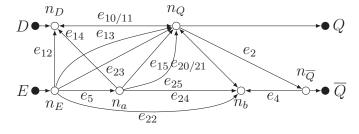

In addition, a new automatic symmetry computation method is presented. This method shows a significant improvement of the symmetry computation for analog circuits, because

- it provides an improved handling of asymmetries, and

- it is the only method that can handle multiple, overlapping differential signal paths correctly.

### 4. A Consistent Constraint Generation Method

Existing constraint generation approaches were revised and generalized. The resulting method can provide consistent constraints for the complete analog design flow with a focus on sizing and placement.

Parts of this work have been published in Eick et al. (2009), Eick, Lu & Graeb (2010), Eick, Strasser, Graeb & Schlichtmann (2010), Strasser et al. (2011), Eick et al. (2011), Eick & Graeb (2011a), Eick & Graeb (2011b), Eick & Graeb (2012a), Eick & Graeb (2012b), Eick & Graeb (2012c), Eick & Graeb (2013), Eick, Sridharan & Graeb (2013) and Eick, Strasser & Lu (2013). Some subproblems and provisional results were investigated in the following student projects: Lu (2009), Stolberg-Stolberg (2009), Stolberg-Stolberg (2010), Tag (2010), Tschöpe (2010), Tsonev (2010), Youssef (2010), Zhang (2011), Guo (2012), Jongudomkarn (2012) and Sridharan (2013).

The remainder of this thesis is organized as follows. The state of the art is discussed in Chapter 2. Chapter 3 discusses the enhanced building block analysis, Chapter 4 introduces the structural signal path analysis and Chapter 5 describes the new symmetry computation method. After that, two different applications are presented. Chapter 6 describes the application to automatic generation of input data of digital standard cells. Chapter 7 discusses the application to automatic constraint generation for analog circuits. The thesis is concluded by Chapter 8.

## 2. State of the Art

This chapter discusses the state of the art in fields related to the topic of the thesis. First, existing structural and behavioral symbolic analysis methods for analog circuits are discussed. Next, sizing and placement constraint generation methods for analog circuits are covered. After that, structural and functional analysis methods for digital circuits are discussed. Some of these methods are capable of determining the logic function out of the circuit structure.

## 2.1. Structural Analysis for Analog Circuits

Two structural analyses types with relevance for this thesis can be identified. Building block analysis computes basic building blocks like simple current mirrors. The symmetries within a circuit are computed by a symmetry analysis.

## 2.1.1. Building Block Analysis

Building block analysis is the problem of finding subcircuits with a fixed topology within a circuit. From a mathematical point of view, this is the problem of finding subgraph isomorphism. Hence, the problem is related to comparing two complete circuits using isomorphism methods. Such methods are applied in layout–versus–schematic (LVS) checks (Barke 1984). The relatively small number and size of analog building blocks allows to develop more specialized methods, which are discussed in the following.

Chen & Sheu (1992) describe an algorithm to recognize differential pairs, simple current mirrors, common-gate devices and cascode current mirrors by identifying four types of special circuit nodes.

Arsintescu (1996) suggests a weighted bipartite matching algorithm to identify simple current mirrors and level shifters (called biasing groups).

Mahmoud (1998) describes a method using pattern rules to recognize certain template circuits. The extent of these templates is unclear. The example shown covers simple current mirrors and a differential pair.

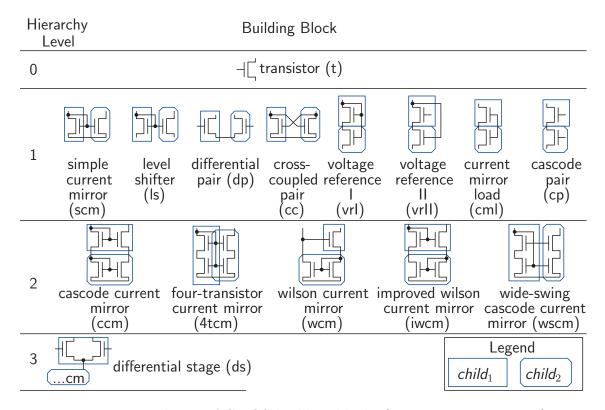

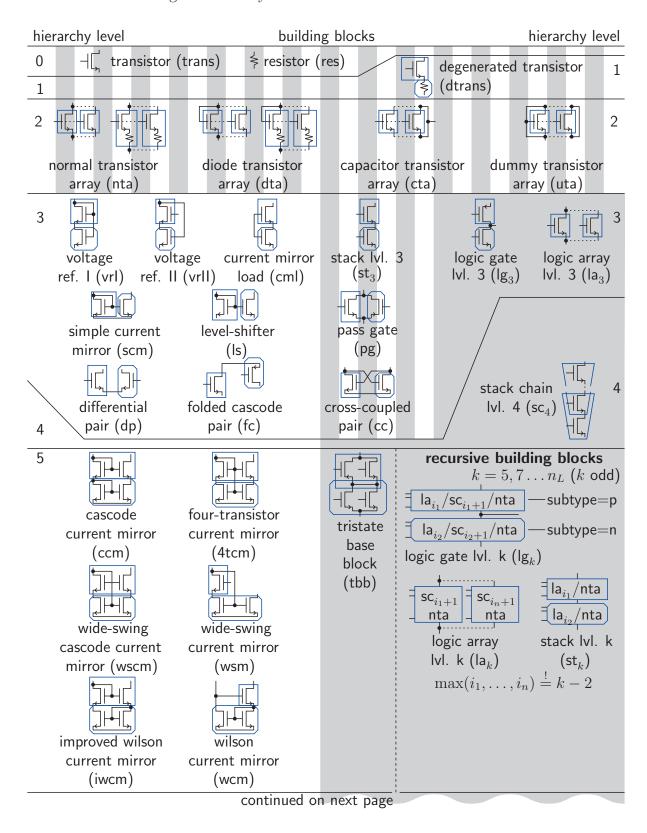

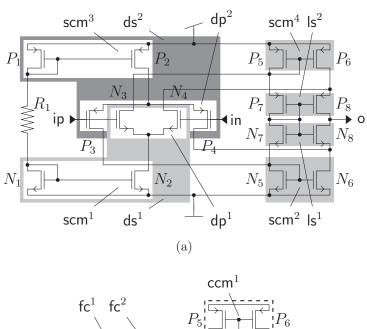

Figure 2.1.: Library of CMOS building blocks (Massier 2010, Fig. 3.2).

#### The Sizing Rules Method

The Sizing Rules Method described by Massier (2010)<sup>1</sup> includes a recognition algorithm that compares a hierarchical building block library to a given netlist. It is the most complete approach with respect to the covered types of building blocks and it is the only approach that can handle CMOS and bipolar circuits. Since this algorithm is the basis for the building block analysis presented in Chapter 3, a more detailed description of this approach is given in the following.

Figure 2.1 shows the CMOS part of the building block library. It consists of four hierarchy levels 0 to 3. Hierarchy level 0 contains a single MOSFET transistor. Hierarchy level 1 contains the pair building blocks simple current mirror, level shifter, differential pair, cross—coupled pair, voltage reference I, voltage reference II, current mirror load and cascode pair. The transistors forming the pair are called children of the building block. They are numbered to allow referencing. In Fig. 2.1 the child with index 1 is marked by a blue rectangle and the child with index 2 is marked by a blue rectangle with beveled corners. Hierarchy level 2 contains building blocks that are built using blocks from hierarchy levels 0 and 1: The cascode current mirror consists of a simple

¹preliminary works in (Graeb et al. 2001, Zizala 2001, Massier 2002, Massier et al. 2003, Eick 2006, Massier et al. 2008a, Massier et al. 2008b, Massier & Graeb 2008)

```

\begin{array}{c|c} 1 & \mathcal{B} \leftarrow \emptyset \\ \\ 2 & \text{for } t \leftarrow \text{scm}, 1\text{s}, \text{dp}, \ldots, \text{ccm}, 4\text{tcm}, \ldots, \text{ds} \\ \\ 3 & X \leftarrow \left\{ (c_1, c_2) \in (\mathcal{B} \cup \mathcal{D})^2 | \text{leftTypeMatches}(t, c_1) \wedge \text{rightTypeMatches}(t, c_2) \right\} \\ \\ 4 & \text{for } (c_1, c_2) \in \left\{ (c_1, c_2) \in X | \text{patternMatches}(t, c_1, c_2) \right\} \\ \\ 5 & \mathcal{B} \leftarrow \mathcal{B} \cup \left\{ \text{newBuildingBlock}(t, (c_1, c_2)) \right\} \\ \\ 6 & \mathcal{B} \leftarrow \text{resolveConflicts}(\mathcal{B}) \\ \\ 7 & \mathcal{B} \leftarrow \text{removeUncertainBuildingBlocks}(\mathcal{B}) \\ \end{array}

```

Figure 2.2.: Building block analysis algorithm according to Massier (2010).

current mirror and a level shifter. The four–transistor current mirror is formed by a voltage reference I and a current mirror load. The wilson current mirror consists of a single transistor and a simple current mirror. The improved wilson current mirror is formed by a simple current mirror and a level shifter. The wide–swing cascode current mirror of a voltage reference II and a cascode pair. Hierarchy level 3 contains the differential stage which is formed by a differential pair and some current mirror.

An outline of the analysis algorithm is given in Fig. 2.2. Set  $\mathcal{B}$  includes all recognized building blocks and set  $\mathcal{D}$  denotes the devices (e.g., transistors) of the circuit. The algorithm iterates over all defined building blocks of hierarchy level 1, 2 and 3. For each iteration, pairs  $(c_1, c_2) \in X$  with matching types are determined first. For example, for the recognition of a simple current mirror, pairs of transistors are formed. For the recognition of a cascode current mirror, pairs  $(c_1, c_2)$  are formed, where  $c_1$  is a simple current mirror and  $c_2$  is a level shifter. Next, the connection patterns of all pairs in X are compared with the connection pattern of the current building block. If the pattern matches, a new building block is created.

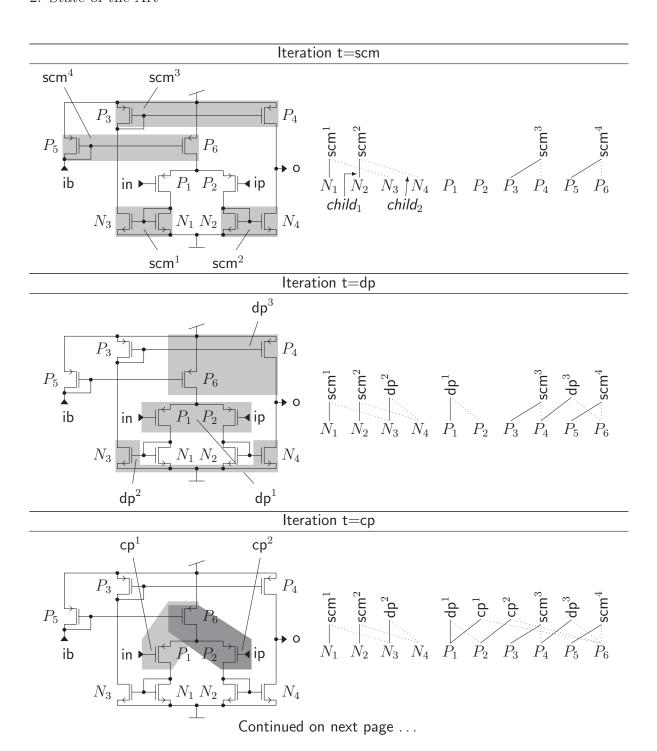

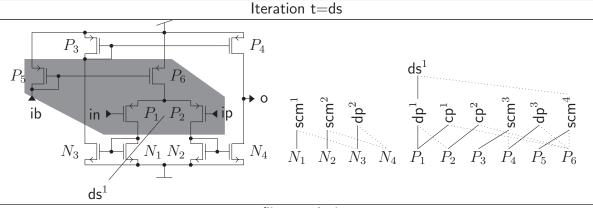

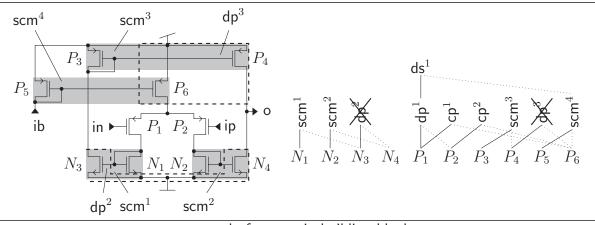

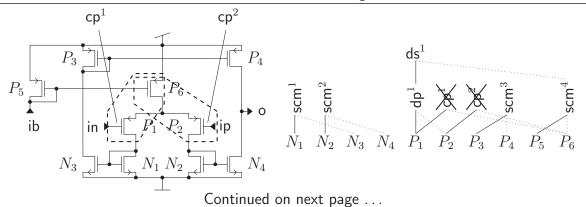

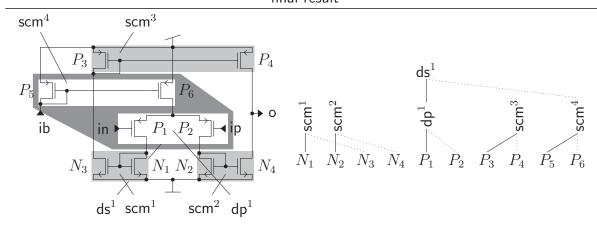

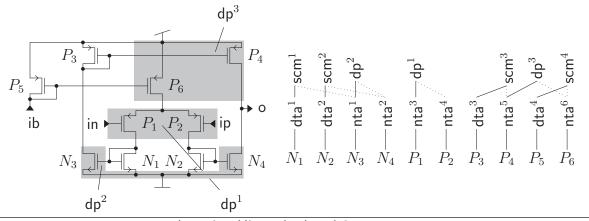

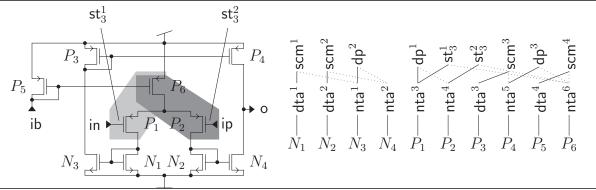

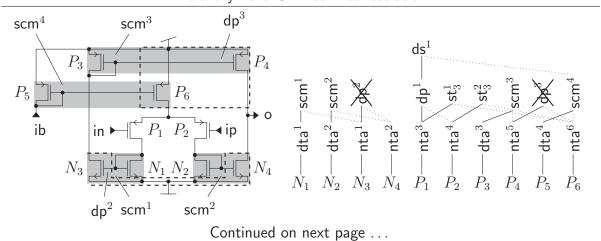

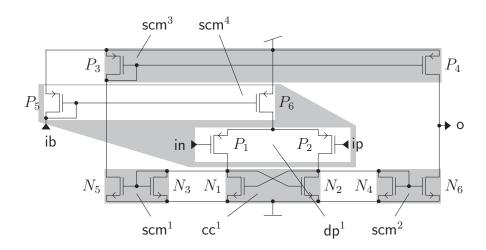

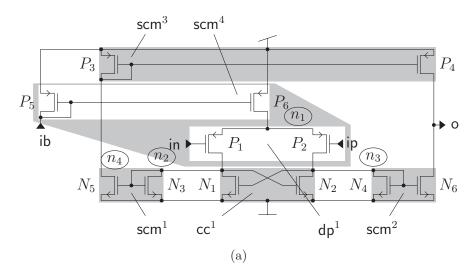

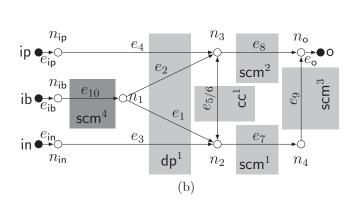

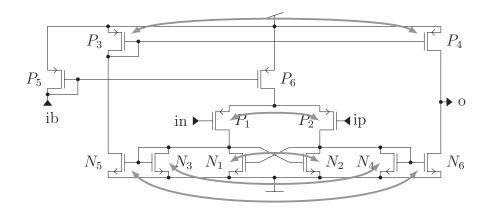

Table 2.1 illustrates the course of the algorithm for the symmetrical OTA from Sansen (2007, Silde 0711). In the iteration for t = scm, four simple current mirrors  $\text{scm}^1$ ,  $\text{scm}^2$ ,  $\text{scm}^3$  and  $\text{scm}^4$  are recognized. They consist of transistors  $N_1$  and  $N_3$ ,  $N_2$  and  $N_4$ ,  $P_3$  and  $P_4$  as well as  $P_5$  and  $P_6$ , respectively. The search for differential pairs (t = dp) yields differential pair  $\text{dp}^1$  consisting of  $P_1$  and  $P_2$ , differential pair  $\text{dp}^2$  consisting of  $N_3$  and  $N_4$  as well as differential pair  $\text{dp}^3$  consisting of  $P_4$  and  $P_6$ . The latter two are false recognitions that will be removed in later steps. Iteration t = cp finds two (false) cascode pairs  $\text{cp}^1$  and  $\text{cp}^2$  consisting of  $P_1$  and  $P_6$  as well as  $P_2$  and  $P_6$ . Finally, one differential stage  $\text{ds}^1$  consisting of  $\text{dp}^1$  and  $\text{scm}^4$  is found in iteration t = ds.

In the example, transistor  $N_3$  is part of scm<sup>1</sup> and dp<sup>2</sup>. The question arises, which of these building blocks is valid and which is wrong. Two building blocks are said to be in conflict if they overlap at least at one device. Formally this can be written as follows. The set of all devices  $D_{\star}(x) \subseteq \mathcal{D}$  of a building block contains all devices that form the

Table 2.1.: Flow of the recognition algorithm for a symmetrical OTA (Sansen 2007, Slide 0711).

## Continued from previous page . . .

## conflict resolution

## removal of uncertain building blocks

Table 2.1.: Flow of the recognition algorithm for a symmetrical OTA (Sansen 2007, Slide 0711).

### Continued from previous page . . .

## final result

Table 2.1.: Flow of the recognition algorithm for a symmetrical OTA (Sansen 2007, Slide 0711).

block. The devices can either be direct children, grandchildren, great-grandchildren, etc. Set  $D_{\star}(x)$  is recursively defined as follows,

$$D_{\star}(x) = \begin{cases} \bigcup_{y \in x. children} D_{\star}(y) & x \in \mathcal{B} \\ \{x\} & x \in \mathcal{D} \end{cases}, \tag{2.1}$$

where  $x.children \subseteq \mathcal{D} \cup \mathcal{B}$  denotes the set of all children of x. In some cases, it is necessary to distinguish the devices that belong to the first child  $x.child_1$  or the second child  $x.child_2$  of a pair. For these cases, sets  $D_1(x)$  and  $D_2(x)$  are defined as follows,

$$D_1(x) := D_{\star}(x.child_1) \qquad D_2(x) := D_{\star}(x.child_2) . \tag{2.2}$$

Index  $\star$  can also be interpreted as 1 or 2 because a pair has exactly two children and

$$D_{\star}(x) = D_1(x) \cup D_2(x) . \tag{2.3}$$

In the example, sets  $D_1(\text{scm}^1)$ ,  $D_2(\text{scm}^1)$  and  $D_{\star}(\text{scm}^1)$  of simple current mirror scm<sup>1</sup> are,

$$D_1(\text{scm}^1) = \{N_1\} \qquad D_2(\text{scm}^1) = \{N_3\} \qquad D_{\star}(\text{scm}^1) = \{N_1, N_3\} \ .$$

(2.4)

For differential pair  $dp^2$ , sets  $D_1(dp^2)$ ,  $D_2(dp^2)$  and  $D_*(dp^2)$  are,

$$D_1(dp^2) = \{N_3\}$$

$D_2(dp^2) = \{N_4\}$   $D_*(dp^2) = \{N_3, N_4\}$ . (2.5)

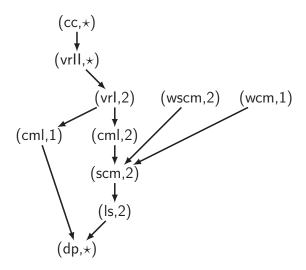

Figure 2.3.: Dominance graph  $G_D$  for the library shown in Fig. 2.1 (Massier 2010, Fig. 4.7).

The assignment of  $N_3$  and  $N_4$  to  $D_1(\mathrm{dp}^2)$  and  $D_2(\mathrm{dp}^2)$  is arbitrary because the differential pair is symmetric. However, set  $D_{\star}(\mathrm{dp}^2)$  is not influenced.

According to Massier (2010), a conflict is resolved by determining a dominant building block that is kept and a dominated building block that is removed using the dominance graph shown in Fig. 2.3. Precisely,

$$x_2$$

dominates  $x_1 :\Leftrightarrow \exists_{(i,j)\in\{1,2,\star\}^2} \left(D_i(x_1) \cap D_j(x_2) \neq \emptyset\right) \land \left((x_1.type,i) \text{ reachable from } (x_2.type,j)\right), (2.6)$

where  $x_1$  type and  $x_2$  type denote the type of building blocks  $x_1$  and  $x_2$ , respectively. Cut–set  $D_i(x_1) \cap D_j(x_2)$  is non-empty if  $x_1$  and  $x_2$  share one device. If i = 1 and j = 2 this device is part of the first child of  $x_1$  and the second child of  $x_2$ . If  $i = \star$  and j = 2 this device is part of the first or second child of  $x_1$  and the second child of  $x_2$ . Relation reachable from is true for  $\mu$  and  $\nu$  iff there is a path in  $G_D$  from  $\nu$  to  $\mu$ . A recognition result described through  $\mathcal{B}$  is said to be conflict free, if there is no building block  $x_2 \in \mathcal{B}$  that dominates some building block  $x_1 \in \mathcal{B}$ ,

$$\forall_{(x_1,x_2)\in\mathcal{B}^2} \overline{x_2 \text{ dominates } x_1} . \tag{2.7}$$

The notation used here differs from the notation used by Massier (2010), but Eq. (2.7) can be shown to be equivalent to Massier (2010, 4.11) (see Appendix B).

In the example, the conflict between  $scm^1$  and  $dp^2$  can now be resolved using Eq. (2.6).

#### 2. State of the Art

For  $x_1 = dp^2$ ,  $x_2 = scm^1$ , i = \* and j = 2, the following holds,

$$\left(D_{\star}(\mathrm{dp^2}) \cap D_2(\mathrm{scm^1}) = \{N_3\} \neq \emptyset\right) \wedge \left((\mathrm{dp}, \star) \text{ reachable from (scm, 2)}\right)$$

$$\Leftrightarrow \mathrm{scm^1 dominates dp^2}. \quad (2.8)$$

The conflict is resolved by removing dp<sup>2</sup>. In the example, there is a second conflict between scm<sup>3</sup>, scm<sup>4</sup> and dp<sup>3</sup>. The conflict is resolved by removing dp<sup>3</sup> (see Table 2.1).

The building blocks differential pair and cascode pair are connected at one point only, e.g., the two transistors of a differential pair are only connected at their source pins. These building blocks are considered as uncertain and are removed if they are not part of a larger building block. In the example, differential pair dp<sup>1</sup> is kept because it is part of differential stage ds<sup>1</sup>. In contrast, cascode pairs cp<sup>1</sup> and cp<sup>2</sup> are removed because they are not part of a larger building block (Table 2.1). The final recognition result for the example is shown at the bottom of Table 2.1.

## 2.1.2. Symmetry Analysis

Symmetry analysis or symmetry computation is the problem of identifying two parts in the netlist of a circuit that should work equally or exactly opposed. The following describes how different authors tackled that problem for different applications in the context of analog circuits.

Charbon et al. (1993) present a symmetry computation to generate matching constraints for layout. It works on an undirected graph where nodes are devices and edges are nets. They propagate pairs of symmetric nodes trough the circuit while considering the results of a sensitivity analysis. The propagation is stopped when a real or virtual ground is reached. According to the experimental results, they can handle one fully-differential or single-ended signal path. This signal path is subdivided into multiple symmetry axes. The algorithm needs a sized netlist to compute the sensitivities.

Kole et al. (1994) describe a symmetry analysis with applications in symbolic analysis and behavioral modeling. They use a hypergraph where nets are nodes and devices are edges. Starting from each node and edge of the circuit their algorithm tries to create two isomorphic trees. The algorithm is limited to fully symmetric circuits. They suggest to handle so-called near symmetries by transforming the circuit to a fully symmetric one. However, it is not explained how this can be automated.

Arsintescu & Spanoche (1996) and Arsintescu (1996) suggest a symmetry computation method for placement constraint generation and visualizing netlists of analog circuits. Their data structure is a bipartite graph with the nets and transistor pins as nodes. Starting from every net in the circuit, they try to propagate pairs of symmetric nodes

trough this graph. Their algorithm includes the sizing, i.e., two transistors are only detected as symmetric if they have the same sizing. They claim that the algorithm can handle circuits that are not fully symmetric. However, they do not describe how the algorithm achieves this.

Yi et al. (2003), Hao et al. (2004) and Zhou et al. (2005) present a symmetry computation with application in placement constraint generation. They use a bipartite graph and a labeling algorithm similar to the Gemini II algorithm (Ebeling 1988). Asymmetries in the circuit are handled by ignoring the gate connections and an initial transformation of the netlist. However, it is unclear if this can be automated in a reliable way.

Bhattacharya et al. (2004) describes an algorithm to extract symmetry constraints from a given layout for retargeting of analog circuits.

## 2.1.3. More Structural Analysis Methods

Other structural analysis methods were suggested in the context of structural synthesis. The purpose of these methods is to detect unrealistic circuit configurations and evaluate the results. Examples can be found in Sripramong & Toumazou (2002), Ferent & Doboli (2010) and Meissner et al. (2012).

## 2.2. Behavioral Analysis

Behavioral analysis methods can be divided into qualitative and quantitative methods. Qualitative methods will give information, e.g., on which path an input signal propagates trough the circuit but will not include information about the exact magnitude of the signal at the output. Quantitative methods will give information about signal magnitudes.

One of the earliest works on qualitative analysis was published in the field of artificial intelligence (de Kleer 1984). It uses causal analysis to generate a qualitative model of a circuit starting from qualitative models of the devices as well as Kirchhoff's Laws. The result is represented as so-called mechanism graph, which represents a sequence of deductions leading to a certain input/output behavior. An algorithm to compute possible current flows trough a circuit is investigated by Hao et al. (2004) and Zhou et al. (2005). They call this signal flow analysis and use it to identity the signal processing part (core part) of the circuit as well as to generate layout constraints. Another so-called signal flow analysis is patented by Zhang et al. (2008). They model possible signal flows on transistor level using a graph. They claim, that this can be used to partition the circuit into a digital part, an analog biasing part and an analog core part. However, they do not present their exact method.

## 2. State of the Art

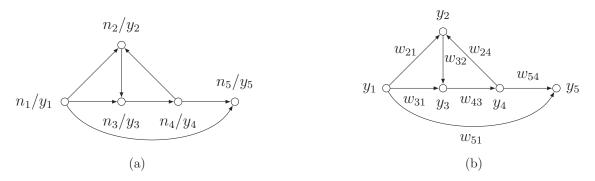

Figure 2.4.: Examples of signal flow graphs. (a) General signal flow graph. (b) Linear signal flow graph.

Quantitative methods can be further subdivided into numerical and symbolic methods. Numerical methods like SPICE simulation are applicable to a wide range of circuits but they do not give insight how a circuit works. Symbolic methods try to find analytical equations to describe the behavior of the circuit (Gielen & Sansen 1991). These models are typically linear and limited to small-signal behavior. A small and simple model may give good insight but have bad accuracy, because important parameters were neglected. A large model may have good accuracy but provide less insight, because it is too complex.

## Signal Flow Graphs

Some symbolic methods use so-called signal flow graphs, which are related to data structures used in this thesis. Signal flow graphs have wide applications in all fields of electrical engineering, e.g., control theory and signal processing. They were first introduced by Mason (1953). The work describes general properties of signal flow graphs as well as linear signal flow graphs. The idea is to represent possible ways of signal propagation between variables represented as nodes of a directed graph. An example is given in Fig. 2.4a. If an edge e connects nodes  $n_i$  and  $n_j$  it means that a signal can propagate from  $n_i$  to  $n_j$ . Thus, in the example a signal can propagate from node  $n_1$  to node  $n_2$  but not from  $n_4$  to  $n_1$ . Every node  $n_i$  processes the input signals to generate one output signal  $y_i$  using a function  $f_i$ . Thus, the example can be written as,

$$y_2 = f_2(y_1, y_4)$$

$y_3 = f_3(y_1, y_2)$   $y_4 = f_4(y_3)$   $y_5 = f_5(y_1, y_4)$ . (2.9)

No expressions for the functions are considered so far. For linear signal flow graphs

the node functions  $f_i$  are linear. For the example this could be,

$$y_2 = w_{21} y_1 + w_{24} y_4$$

$y_3 = w_{31} y_1 + w_{32} y_2$   $y_4 = w_{43} y_3$   $y_5 = w_{51} y_1 + w_{54} y_4$ . (2.10)

For convenience the edges of the graph can be labeled with the weights of the corresponding inputs and the nodes can be labeled with the variables (Fig. 2.4b). The total transfer function or gain from node  $n_i$  to another node  $n_j$  can then be computed using simplification steps (Mason 1953) or Mason's Rule (Mason 1956). The latter allows to compute the transfer function by analyzing loops and forward paths. Forward paths connect input to output and do not contain any node twice. If there is only one feedback loop with loop gain T, Mason's Rule can be written as,

$$\frac{\sum_{i} G_{i} + \sum_{i} H_{i} (1 - T)}{(1 - T)}, \qquad (2.11)$$

where  $G_i$  is the gain of the i-th forward path touching the loop and  $H_i$  is the gain of the i-th forward path not touching the loop. A more general formulation for multiple loops can be found in Mason (1956). Using this, the gain from node  $y_1$  to node  $y_5$  can be calculated for the example. The graph has one loop consisting of nodes  $y_2$ ,  $y_3$  and  $y_4$  with loop gain  $T_1 = w_{32} w_{43} w_{24}$ . The graph has three forward paths. Paths  $y_1, y_2, y_3, y_4, y_5$  and  $y_1, y_3, y_4, y_5$  touch the loop. Their gains are  $G_1 = w_{21} w_{32} w_{43} w_{54}$  and  $G_2 = w_{31} w_{43} w_{54}$ , respectively. Path  $y_1, y_5$  does not touch the loop. Its gain is  $H_1 = w_{51}$ . In this case Mason's Rule evaluates to

$$\frac{y_5}{y_1} = \frac{G_1 + G_2 + H_1(1 - T)}{1 - T}

= \frac{w_{31} w_{43} w_{54} + w_{21} w_{32} w_{43} w_{54} + w_{51}(1 - w_{32} w_{43} w_{24})}{1 - w_{32} w_{43} w_{24}} .$$

(2.12)

Linear signal flow graphs are used by many symbolic analysis approaches for analog circuits (Gielen & Sansen 1991). Since the nodes of the signal flow graph are the variables of the problem, structural information is lost. This is different for the graph proposed by Wei & Doboli (2008). The nodes of this so-called coupled building-block behavioral (CBBB) model are the nets of the circuit. The edges and the corresponding linear expressions are generated based on the building blocks of the circuit. However, structural information is not considered during subsequent analysis. They present also a variant called uncoupled building-block behavioral (UBBB) model, where feedbacks are removed and a method to handle weakly non-linear circuits.

# 2.3. Constraint Generation for Analog Circuits

Constraint generation and constraint management has been discussed in several publications.

#### 2. State of the Art

| Approach                                                               |                 | Analyses |               |               | Generated Constraints     |                                                              |

|------------------------------------------------------------------------|-----------------|----------|---------------|---------------|---------------------------|--------------------------------------------------------------|

|                                                                        | building blocks | symmetry | sensitivities | current flows | sizing                    | layout                                                       |

| Chen & Sheu (1992)                                                     | ×               |          | ×             |               | _                         | matching net length net spacing                              |

| Charbon et al. (1993)<br>Choudhury &<br>Sangiovanni-Vincentelli (1996) | 1993)           | ×        | ×             |               |                           | matching parasitics layout symmetry                          |

| Arsintescu &<br>Spanoche (1996)                                        | ×               | ×        |               |               | _                         | matching layout symmetry                                     |

| Graeb et al. (2001)<br>Massier et al. (2008b)<br>Massier (2010)        | ×               |          |               |               | operating region matching | _                                                            |

| Yi et al. (2003)<br>Hao et al. (2004)<br>Zhou et al. (2005)            | ×               | ×        |               | ×             |                           | matching<br>layout symmetry<br>core/bias identi-<br>fication |

Table 2.2.: Overview of constraint generation approaches for analog circuits

General concepts for so-called constraint—driven design were discussed in the introduction. Krinke & Lienig (2011) present a formal approach to constraint definition using so—called ontologies. Malavasi & Kao (1997) discuss different challenges for constraint—driven physical design, including noise, delay, parasitics, symmetries, matching and yield. Malavasi et al. (1998) present a general constraint management system.

Some approaches to automatic constraint generation were published together with the structural analysis methods discussed in Section 2.1. They are summarized in Table 2.2. It can be observed that various approaches exist to generate layout constraints. They utilize different combinations of building block, symmetry, sensitivity and current flow analyses. The constraints generated cover matching, net length, net spacing, bounds for parasitics, layout symmetry and special restrictions for the core part. Apart from that, there is one approach (Massier 2010) to generate operating region and matching constraints for sizing by analyzing building blocks.

A method to identify critical and less critical constraints during constraint transformation was presented by Arsintescu & Otten (1998). Arsintescu et al. (1998) present

a method to transform AC constraints between different abstraction levels. Makris & Toumazou (1995) present a method based on qualitative reasoning to correct a circuit in case the specification is violated. Some approaches to transform constraints from one level of a design hierarchy to another were investigated in the context of analog circuit synthesis. BLADES (El-Turky & Perry 1989) and OASYS (Harjani et al. 1989) suggest knowledge—based approaches.

## 2.4. Structural Analysis for Digital Circuits

Structural analysis of digital circuits was broadly covered by research in the past. The following discusses recognition of digital building blocks (e.g., inverters), computation of true signal flow of switches and regularity extraction.

For the recognition of digital building blocks two classes of approaches exist: library based approaches and algorithmic approaches.

Library based approaches typically model circuit and building blocks in a library using graphs. Subgraph isomorphism algorithms are applied to compare the building blocks from the library to the circuit (Watanabe et al. 1983, Huang & Overhauser 1995, Rubanov 2003, Rubanov 2006, Zhang & Wunsch II 2006). These methods are independent of a specific design style like CMOS. However, their recognition ability is limited to building blocks contained in the library.

Algorithmic approaches use the design rules of a specific design style like CMOS logic to interpret a given netlist. Some approaches for CMOS logic investigate series and parallel connection in the pull-up and pull-down network (Takashima et al. 1982, Boehner 1988, Yokomizo et al. 1990, Dagenais 1991, Kim & Shin 1998). Bryant (1991) extends this concept using four valued logic considering high impedance and unknown states. Other approaches investigate paths of serial transistors ending at the power rails (Laurentin et al. 1992, Hübner et al. 1997). All approaches compute the logic function of the gate. These approaches can cover one design style (typically CMOS logic) completely, but cannot be used for other design styles.

A hybrid approach is presented by Yang & Shi (2003). They speed-up a subgraph isomorphism approach by preprocessing the netlist using an algorithmic approach to identify simple gates.

In case sequential circuits are investigated it must be considered that states are saved internally. The variables in the resulting logic function can refer to different time steps, leading to so–called temporal logic (Ari et al. 1983). Pandey et al. (1995) and Jain et al. (1995) show how state machines can be extracted using symbolic simulation.

The problem of determining the correct signal flow within switches, e.g., pass gates or pass transistors, occurs for example in switch-level simulation and timing verification.

## 2. State of the Art

The approach of Jouppi (1983) relies on a set of local rules. Ousterhout (1985) suggest to search paths between the switch and a strong signal source. Other approaches represent the circuit as graph and classify the nodes according to different criteria (Blaauw et al. 1990, Lee et al. 1990, Baba-ali & Farah 1996). Next, switch directions are determined using local rules as well as reachability analysis on the graph.

Many EDA algorithms for digital circuits can be speeded up by exploiting regularities and symmetries. Regularity extraction tries to find repetition of the same subcircuit within one circuit. The extent of this subcircuit is not known in the beginning. Regularity extraction algorithms work in two steps: First, subcircuit candidates are identified using heuristics. Second, repetitions of these subcircuits within the circuit are searched using the subgraph isomorphism techniques described above (Rao & Kurdahi 1993, Hassoun & McCreary 1999). Symmetry extraction was investigated based on general automorphism approaches (Aloul et al. 2002) as well as using special heuristics (Wang et al. 2003, Chai 2009). None of these approaches is suitable for analog circuits because appropriate heuristics are not known and the general approaches can not handle cases that are not fully symmetric.

# 3. Enhanced Building Block Analysis

The idea of building block analysis is that most integrated analog and digital circuits are composed out of a few basic building blocks of fixed topology. Although these building blocks are small they make up the essential circuit functions. Typical examples of analog building blocks are current mirrors and differential pairs. Typical examples of digital building blocks are inverters or NAND gates. Building block analysis tries to identify such building blocks in a given circuit. The results can then be fed to other analyses allowing, e.g., automatic constraint generation.

In the following, a new building block analysis method is presented. It consists of a new building block library containing analog and digital building blocks, the corresponding ambiguity resolution graph and a new algorithm to handle this library. The chapter is concluded by a discussion of the contributions compared to the state of the art and by experimental results.

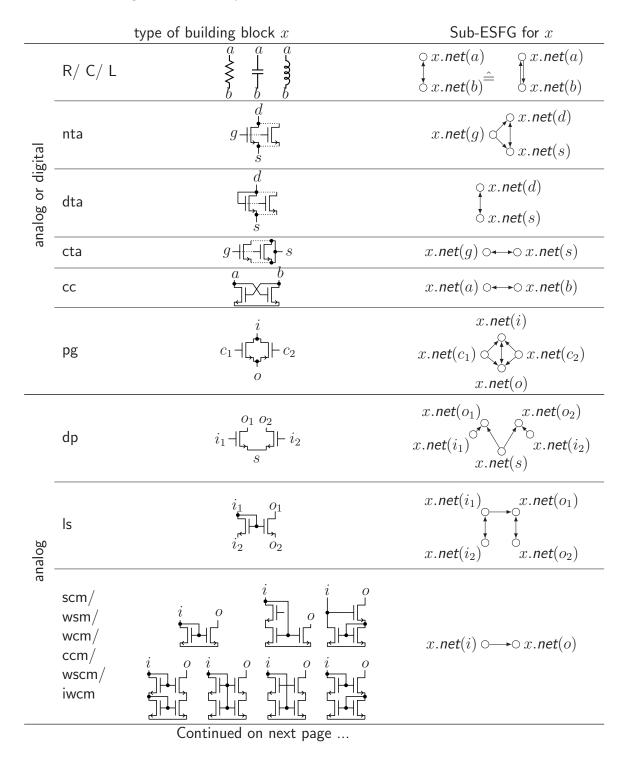

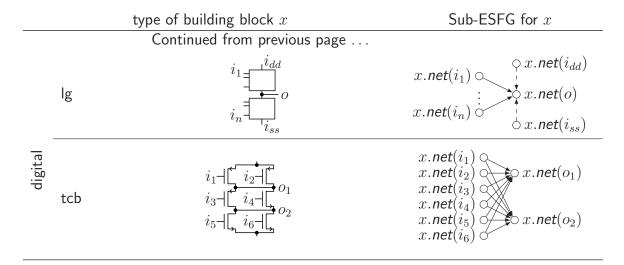

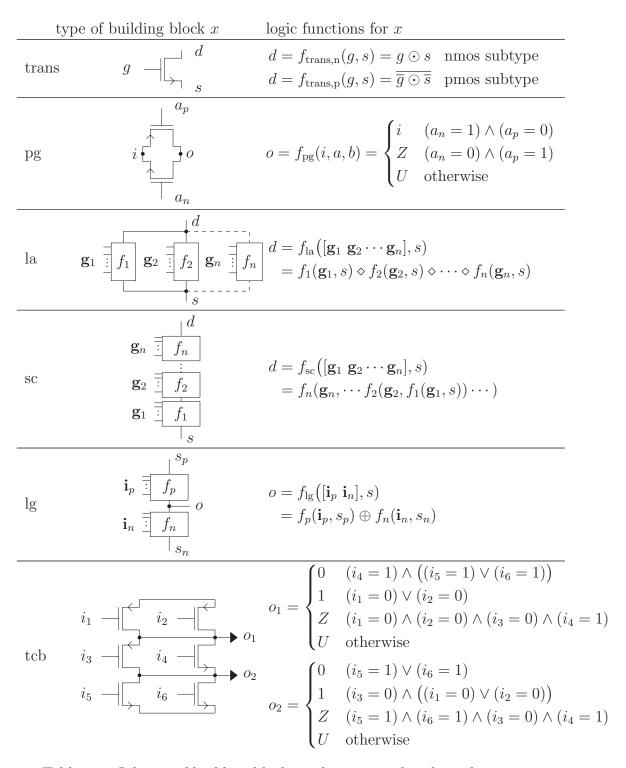

## 3.1. Library of Analog and Digital Building Blocks

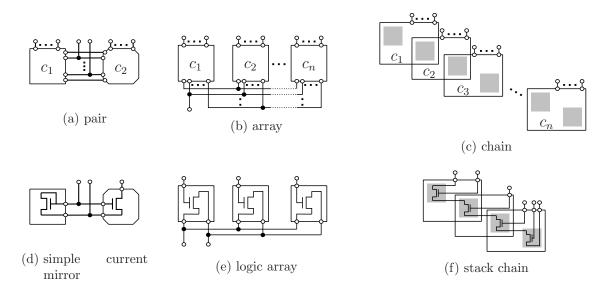

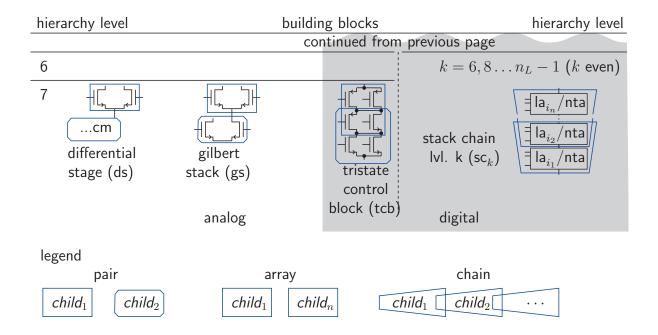

The library is shown in Fig. 3.2. The library is organized in a hierarchical way. Each building block in the library consists of devices (e.g., transistors) or other building blocks. Each building block and each device has a number of pins that connect to the nets of the circuit. The building blocks can be distinguished according to the following criteria:

#### • Hierarchy level

The library is partitioned into  $n_L$  hierarchy levels. The building blocks from one hierarchy level are built out of building blocks from lower hierarchy levels. The overall number of hierarchy levels  $n_L$  depends on the size of the logic gates used. The presented algorithm will determine the correct value of  $n_L$  automatically.

# • Generic building block type The building blocks in the library are of three different generic building block types:

#### - Pair

A pair is formed by exactly two children  $c_1$ ,  $c_2$ , which are building blocks or devices of different or equal type (Fig. 3.1a). At least one pin of child  $c_1$  must be connected to one pin of child  $c_2$ . The pins of the pair can be formed by connected and unconnected pins of  $c_1$  and  $c_2$ . An example is a *simple*

## 3. Enhanced Building Block Analysis

Figure 3.1.: Generic building block types ((a) to (c)) and corresponding examples ((d) to (f)).

current mirror (Fig. 3.1d). Child  $c_1$  is a diode–connected transistor (more specifically a diode transistor array) and child  $c_2$  is a transistor without self connections (more specifically a normal transistor array). Both children are connected at their gate and source pins. The input pin of the overall simple current mirror is connected to the gate pins of both children. The source pin of the simple current mirror is connected to the source pins of both children. The output pin of the simple current mirror is connected to the drain pin of the second child.

## - Array

An array is formed by n children  $c_1$  to  $c_n$  which are building blocks or devices of equal type (Fig. 3.1b). All children are connected in parallel by one or more nets. The pins of the pair can be formed by connected and unconnected pins of  $c_1$  to  $c_n$ . An example is a logic array with three children (Fig. 3.1e) from level 3 of the library in Fig. 3.2. It consists of transistors without self connections (normal transistor arrays). Drain pins and source pins of all three transistors are connected together and form pins of the logic array. The gates of the transistors form three additional pins of the logic array.

## - Chain

A chain is formed by n children  $c_1$  to  $c_n$  which are pairs of equal type (Fig. 3.1c). For two children  $c_i$ ,  $c_{i+1}$ ,  $i = 1 \dots (n-1)$  the following applies: The second child of  $c_i$  is the first child of  $c_{i+1}$ , i.e.,  $c_i$  and  $c_{i+1}$  share one child. The pins of the chain are formed by the pins of  $c_1$  to  $c_n$ . An example is a stack chain with three children (Fig. 3.1f) from level 4 of the library in

Fig. 3.2. It consists of three stacks on level 3 that overlap at one transistor. The pins of the stack chain are formed by all gate pins, the drain pin of the first transistor and the source pin of the last transistor.

## • Signal type

Building blocks that are only used for analog signals are shown in the unshaded part of the library. The gray shaded part contains building blocks that are only used for digital signals. Building blocks that can be used in both cases are part of the striped part.

## • Subtype

For all building blocks except pass gate, logic gate and tristate control block an NMOS and a PMOS subtype exists. This denotes whether the building block is built out of NMOS or PMOS transistors. In general, only the NMOS subtype is shown in Fig. 3.2.

A description of the different hierarchy levels follows.

## 3.1.1. Hierarchy levels 0 and 1

Hierarchy level 0 contains the devices transistor (trans) and resistor (res). It also can contain other devices like capacitors or inductors but they are not shown in Fig. 3.2.

Hierarchy level 1 contains one pair consisting of a transistor and a resistor. Such a pair is known as degenerated transistor (dtrans) (Johns & Martin 1997).

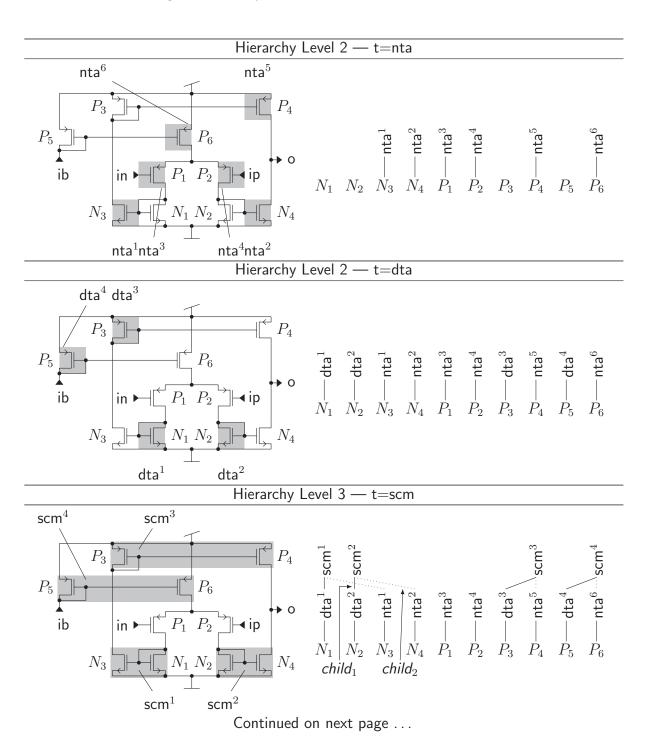

### 3.1.2. Hierarchy level 2

Hierarchy level 2 contains four kind of arrays that pool parallel transistors together based on the connection of the transistor with itself. The normal transistor array (nta) consists of transistors or degenerated transistors (dtrans), where all pins connect to different nets. Transistors or degenerated transistors (dtrans), where gate and drain are connected, form diode transistor arrays (dta). A capacitor transistor array (cta) contains transistors where drain and source are connected. Transistors where all pins are connected, form dummy transistor arrays (uta). All of these array types are allowed to have one child only, i.e., they are also used for single transistors, which have the required connections.

## 3. Enhanced Building Block Analysis

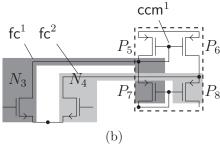

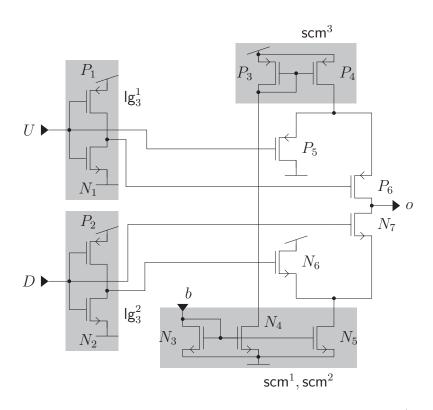

Figure 3.2.: Building block library

Figure 3.2.: Building block library

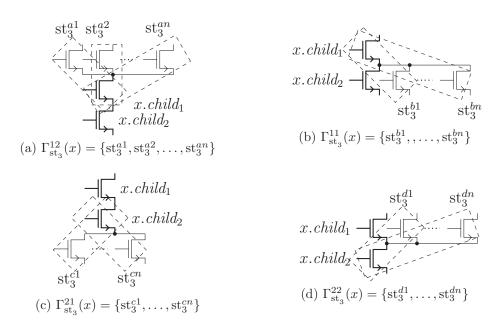

## 3.1.3. Hierarchy level 3

The analog part of hierarchy level 3 contains the pairs voltage reference I (vrI), voltage reference II (vrII), current mirror load (cml), simple current mirror (scm), level shifter (ls), differential pair (dp) and folded cascode pair (fc). They are built of normal transistor arrays and diode transistor arrays. The pairs stack on level 3 (st<sub>3</sub>), pass gate (pg) and cross-coupled pair (cc) can be used in analog and digital circuits. They consist of normal transistor arrays. Pairs logic gate on level 3 (lg<sub>3</sub>) and logic array on level 3 (la<sub>3</sub>) are used in digital circuits only.

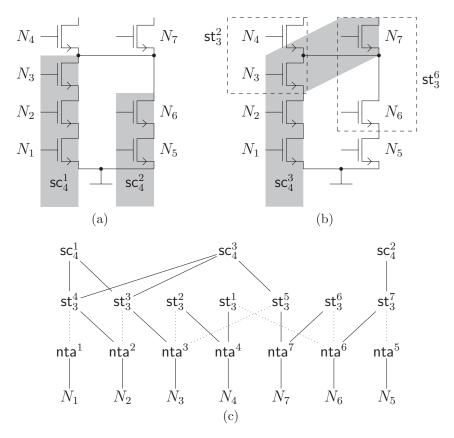

#### 3.1.4. Hierarchy level 4

Hierarchy level 4 contains a stack chain on level 4 ( $sc_4$ ), which is constructed from stacks from level 3 that overlap at one transistor. It is used for digital circuits only.

## 3.1.5. Hierarchy level 5 (non-recursive part)

The analog part of hierarchy level 5 contains several larger current mirrors. A cascode current mirror (ccm) consists of a simple current mirror and a level shifter. A four-transistor current mirror (4tcm) is built out of a voltage reference I and a current mirror load. A wide-swing cascode current mirror (wscm) and a wide-swing current

## 3. Enhanced Building Block Analysis

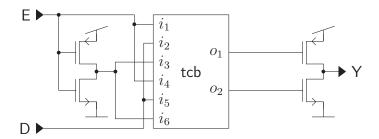

mirror (wsm) are formed by a voltage reference II and a cascode pair or normal transistor array, respectively. An improved wilson current mirror (iwcm) and a wilson current mirror (wcm) consist of a simple current mirror plus a level shifter or normal transistor array, respectively. The digital part of level 5 contains the tristate base block (tbb), consisting of a pass gate and a logic array. It is required to handle one type of tristate cells correctly.

## 3.1.6. Hierarchy level 7 (non-recursive part)

The analog part of hierarchy level 7 contains the differential stage (ds), which consists of some current mirror plus a differential pair, as well as the Gilbert stack (gs), which consists of two differential pairs. It is required for Gilbert-type mixers (Vallee & Masry 1994). The digital part contains the tristate control block (tcb), consisting of two complementary tristate base blocks.

## 3.1.7. Hierarchy levels $5, 7, \ldots, n_L$ (recursive part)

Some of the digital building blocks in all hierarchy levels starting from level 5 are defined recursively. This allows to handle all CMOS circuits without explicitly specifying all possible variants. These building blocks are *logic gate*, *logic array*, *stack* and *stack chain*.

A stack  $(st_k)$  on one of the odd hierarchy levels  $k = 5, 7, 9, \ldots$  can be formed out of logic arrays or normal transistor arrays. At least one of the children must be from level k-2, while the other can be from any level less than k. The same principle applies to logic arrays  $(la_k)$ , which are built of stack chains or normal transistor arrays, as well as logic gates  $(lg_k)$ , which are formed by stack chains, logic arrays or normal transistor arrays. One of these building blocks must be of PMOS subtype and one must be of NMOS subtype.

## **3.1.8.** Hierarchy levels $6, 8, \ldots, n_L - 1$ (recursive part)

Even hierarchy levels  $k = 6, 8, 10, \ldots$  contain stack chains  $(sc_k)$  which are formed by stacks from level k - 1.

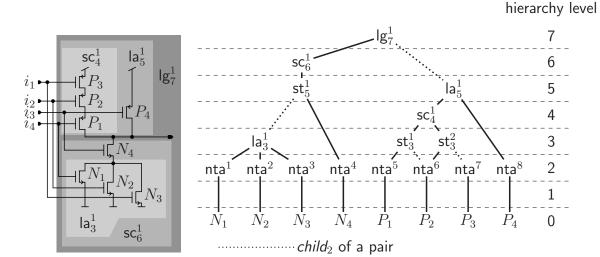

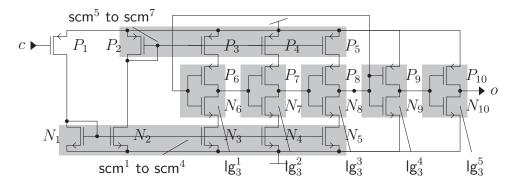

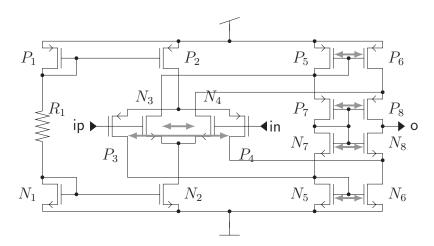

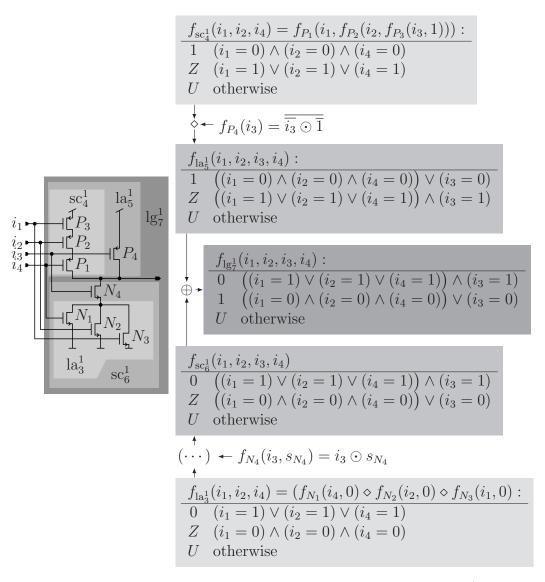

#### **3.1.9.** Example

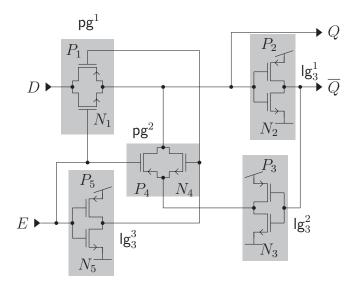

Figure 3.3 illustrates how a compound gate (Weste & Harris 2005, Fig. 1.18) can be represented using the library. The gate consists of PMOS transistors  $P_1$  to  $P_4$  and NMOS transistors  $N_1$  to  $N_4$ . Each transistor is represented by normal transistor arrays

Figure 3.3.: Compound gate (Weste & Harris 2005, Fig. 1.18) with recognized building blocks.

nta<sup>1</sup> to nta<sup>8</sup> on hierarchy level 2. On hierarchy level 3,  $logic \ array \ la_3^1$  consisting of  $N_1$ ,  $N_2$  and  $N_3$  is formed.  $Stack \ st_3^1$  consists of  $P_1$  and  $P_2$ .  $Stack \ st_3^2$  consists of  $P_2$  and  $P_3$ . Since  $st_3^1$  and  $st_3^2$  share  $P_2$ , they form  $stack \ chain \ sc_4^1$  on hierarchy level 4. On hierarchy level 5,  $sc_4^1$  and  $P_4$  form  $logic \ array \ la_5^1$ .  $Stack \ st_5^1$  is built of  $la_3^1$  and  $la_4^2$ . It becomes  $stack \ chain \ sc_6^1$  on hierarchy level 6. Finally,  $logic \ gate \ lg_7^1$  is formed by  $sc_6^1$  and  $la_5^1$  on hierarchy level 7.

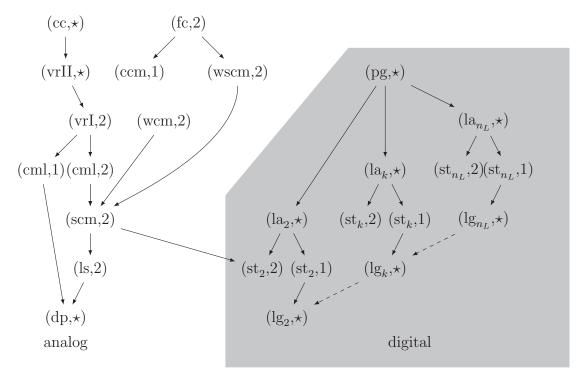

## 3.1.10. Dominance graph

Ambiguities can occur when comparing the library to the circuit. One transistor can become part of multiple, conflicting building blocks. In these cases it must be decided which building block is the correct one. For this purpose, the ambiguity resolution concept of Massier (2010) (see Section 2.1.1) is used. However, a new dominance graph is required for the extended library. The new dominance graph is shown in Fig. 3.4. The analog part of this graph essentially matches the dominance graph proposed by Massier (2010) (Fig. 2.3). A small modification is made to include the folded cascode pair. It dominates the level shifter part of a cascode current mirror and the output part of a wide–swing cascode current mirror. This avoids that transistors of folded cascodes are hidden in cascode current mirrors and wide–swing cascode current mirrors. This is preferable for the structural signal path analysis discussed in Chapter 4.

Inside each level of the digital, recursive part of the library the following holds: The first device or building block of a *stack* dominates a *logic gate*. In the example of Fig. 3.3 this, e.g., prevents a false inverter consisting of  $P_1$  and  $N_4$ . A *logic array*

#### 3. Enhanced Building Block Analysis

Figure 3.4.: Dominance graph for the building block library from Fig. 3.2.

dominates a *stack*. In addition, *logic gates* from higher hierarchy levels dominate *logic gates* from lower hierarchy levels. This means, in case different *logic gates* of different sizes can be formed, the largest one is selected. Transistors that are part of a *pass gate* must not be part of any other building block.

Currently, there is only one connection between the analog and the digital part. The simple current mirror dominates a stack. However, further research in the area of mixed-signal circuits might reveal more dependencies.

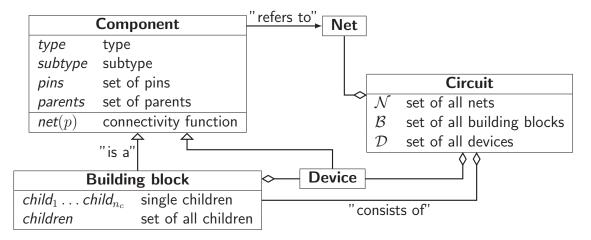

# 3.2. Enhanced Algorithm

Below, a formal notation of a circuit is introduced and the algorithm is described. Figure 3.5 gives an overview of the data structures using a pseudo object-oriented description. A circuit consists of a set of devices  $\mathcal{D}$ , a set of building blocks  $\mathcal{B}$  and a set of nets  $\mathcal{N}$ . Building blocks and devices can be abstracted as components. They share the attributes listed under component in Fig. 3.5. In the following, attributes are denoted in a pseudo object-oriented manner, e.g., c.type denotes the type attribute type of component c. In case a component c is a device, its type c. type is in the set  $T_{\mathcal{D}}$  of device types,

$$c.type \in T_{\mathcal{D}} = \{ trans, res, \ldots \},$$

(3.1)

Figure 3.5.: Data structures representing a circuit.

where trans stands for transistor and res stands for resistor. In case a component c is a building block, its type c.type is in library–dependent set  $T_{\mathcal{B}}$  of all building block types,

$$c.type \in T_{\mathcal{B}}$$

. (3.2)

The subtype c. subtype of a component c denotes whether it is NMOS or PMOS, i.e.,

$$c.subtype \in \{--, n, p\}, \qquad (3.3)$$

where n stands for NMOS, p stands for PMOS and — stands for none. The set of pins c.pins lists all pins of a component c. It depends on the type of the component. For example,  $N_1.pins = \{sc, gt, dn\}$  for a transistor  $N_1$ . The relation between nets and pins of a component c is given by connectivity function

$$c.net(p): c.pins \to \mathcal{N}$$

. (3.4)

Pin p of component c connects to net n iff c.net(p) = n.

A building block  $b \in \mathcal{B}$  is formed by several components. In the following, these components will be denoted as children. They are denoted by attributes  $b.child_1, b.child_2, \ldots$ ,  $b.child_{n_c}$ . The set of all children of a building block b is given by,

$$b.children = \{b.child_1, b.child_2, \dots, b.child_{n_c}\} \subseteq (\mathcal{D} \cup \mathcal{B})$$

(3.5)

If a component a is child of a building block b then b is denoted as parent of a. It holds,

$$a \in b.children \Leftrightarrow b \in a.parents \qquad a.parents \subseteq \mathcal{B}$$

, (3.6)

Figure 3.6.: Enhanced building block analysis algorithm.

where a.parents is the set of all parents of a.

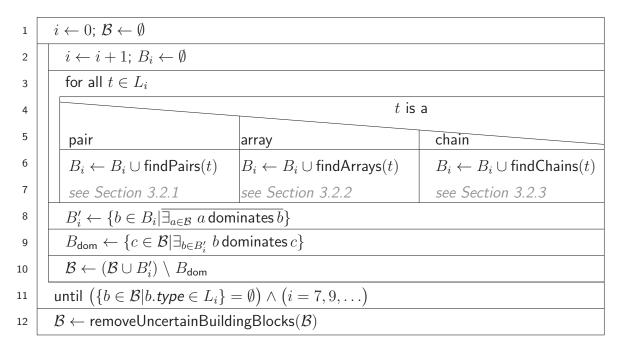

The enhanced building block analysis algorithm is shown in Fig. 3.6. The outer loop (lines 2 to 11) iterates over the different hierarchy levels i of the building block library. Set  $L_i$  contains the building block types of level i,

$$L_i \subseteq T_{\mathcal{B}}$$

(3.7)

For example  $L_2$  for hierarchy level 2 is,

$$L_2 = \{nta, dta, cta, uta\}. \tag{3.8}$$

The outer loop ends if no new building blocks were found in the current hierarchy level. The termination condition is checked in level seven for the first time. This guarantees that all non-recursive building blocks are recognized. After that, the condition is evaluated at all odd hierarchy levels because we expect to find a *logic gate* at the very end. *Logic gates* are part of the odd hierarchy levels 3, 5, . . . (see Fig. 3.2).

Inside each hierarchy level, the inner loop (lines 3 to 7) iterates over all building block types belonging to that level. Depending whether the current type is a pair, array or chain, corresponding functions are called to find new building blocks (line 6). These functions are described in detail in Sections 3.2.1 to 3.2.3.

After that, the dominance relation is evaluated with respect to the found building blocks. Line 8 checks whether the new building blocks are already dominated by some

existing building block. Line 9 computes the set of all existing building blocks that are dominated by the new building blocks. Relation *dominates* corresponds to Eq. (2.6). Finally, the set of all building blocks is updated.

After termination of the main loop all uncertain building blocks that do not have parents are removed similar to the algorithm of Massier (2010) (see Section 2.1.1).

### 3.2.1. Recognition of Pairs

In the following, the algorithm to find pairs is described. It is controlled by a rule function  $\rho_t : (\mathcal{D} \cup \mathcal{B})^2 \to \mathbb{B}$ , where  $\mathbb{B} = \{0,1\}$  is the set of Boolean numbers. Two components  $x_1$  and  $x_2$  are recognized as pair of type t if  $\rho_t$  is true. The available conditions cover required and forbidden connections, required types and subtypes as well as existence of parents. For example, the rule function  $\rho_{scm}$  for a simple current mirror reads as follows.

$$\rho_{\text{scm}}(x_1, x_2) = \underbrace{\left(\underbrace{x_1.type = \text{dta}}\right) \land \left(\underbrace{x_2.type = \text{nta}}\right)}_{\text{type}} \land \underbrace{\left(\underbrace{x_1.subtype = x_2.subtype}\right)}_{\text{same subtype}} \land \underbrace{\left(\underbrace{x_1.net(\text{gt}) = x_2.net(\text{gt})}\right) \land \left(\underbrace{x_1.net(\text{gt}) = x_2.net(\text{dn})}\right)}_{\text{required connections}} \land \underbrace{\left(\underbrace{x_1.net(\text{gt}) \neq x_2.net(\text{dn})}\right)}_{\text{forbidden connection}}$$

$$(3.9)$$

The type conditions require the first component to be a diode transistor array and the second component to be a normal transistor array. Both components must have the same subtype. The required connection conditions require the gates and sources of both components to be connected. The forbidden connection condition forbids a connection between the gate of the first component, which is the drain at the same time, and the drain of the second component.

In order to speed up the recognition algorithm, the rule function is split up into three partial rule functions, for the first child, for the second child and the pair

$$r_{1,t}: \mathcal{N} \times (\mathcal{D} \cup \mathcal{B}) \to \mathbb{B} \quad r_{2,t}: \mathcal{N} \times (\mathcal{D} \cup \mathcal{B}) \to \mathbb{B} \quad r_{12,t}: (\mathcal{D} \cup \mathcal{B})^2 \to \mathbb{B}$$

(3.10)

such that

$$\rho_t(x_1, x_2) \Leftrightarrow \exists_{n \in \mathcal{N}} [r_{1,t}(n, x_1) \land r_{2,t}(n, x_2)] \land r_{12,t}(x_1, x_2).$$

(3.11)

For example the rule function  $\rho_{\text{scm}}$  for a simple current mirror can be rewritten to

$$r_{1,\text{scm}}(n, x_1) \Leftrightarrow (x_1. type = \text{dta}) \land (x_1. net(\text{gt}) = n)$$

(3.12)

$$r_{2,\text{scm}}(n, x_2) \Leftrightarrow (x_2. type = \text{nta}) \land (x_2. net(\text{gt}) = n)$$

(3.13)

$$r_{12,\text{scm}}(x_1, x_2) \Leftrightarrow (x_1.subtype = x_2.subtype) \land (x_1.net(\text{gt}) \neq x_2.net(\text{dn}))$$

$$\land (x_1.net(\text{sc}) = x_2.net(\text{sc}))$$

(3.14)

In general, the rule functions for any pair type t can be determined from the library in Fig. 3.2 as follows:

- 1. One of the connections between both children is selected as characteristic connection. If possible, connections should be avoided that correspond to a power net.

- 2. Function  $r_{1,t}$  for the first child is formed by a type rule for the first child plus the corresponding part of the required connection rule for the characteristic connection.

- 3. Function  $r_{2,t}$  for the second child is formed by a type rule for the second child plus the corresponding part of the required connection rule for the characteristic connection.

- 4. All other conditions form function  $r_{12,t}$ :

- a) A required connection rule for every connection shown in Fig. 3.2 except the characteristic connection.

- b) A forbidden connection rule for every connection not shown in Fig. 3.2.

- c) A same subtype rule if only NMOS transistors are shown in Fig. 3.2. If the building block consists of NMOS and PMOS transistors, corresponding subtype rules are added.

- d) For all recursive building blocks, a rule is added that forbids that children already have parents.

Based on the formulation of recognition rules as function  $r_{1,t}$ ,  $r_{2,t}$  and  $r_{12,t}$  the algorithm can be implemented as shown in Fig. 3.7. A set X of candidate pairs is determined by iterating over all nets (lines 2 to 5). For each net, a candidate set  $X_1$  is computed that contains only components where  $r_{1,t}$  is true. Afterward,  $X_2$  is computed analogously. This can be implemented efficiently by keeping an appropriate index for each net. For all resulting pairs in  $X_1 \times X_2$  and thus for all pairs in X the existence condition in Eq. (3.11) is fulfilled. Thus, a new pair can be created for all pairs in X where  $r_{12,t}$  is fulfilled (lines 6 and 7).

```

findPairs(t)

1

B \leftarrow \emptyset; X \leftarrow \emptyset

2

for all n \in \mathcal{N}

3

X_1 \leftarrow \{x_1 \in \mathcal{D} \cup \mathcal{B} | r_{1,t}(n, x_1)\}

X_2 \leftarrow \{x_2 \in \mathcal{D} \cup \mathcal{B} | r_{2,t}(n, x_2)\}

4

5

X \leftarrow X \cup (X_1 \times X_2)

6

for all (x_1, x_2) \in \{(x_1, x_2) \in X | r_{12,t}(x_1, x_2) \}

7

B \leftarrow B \cup \{\mathsf{newPair}(t, x_1, x_2)\}

8

return B

```

Figure 3.7.: Algorithm to find pairs.

For the worst–case and average runtime complexity of the algorithm, the following considerations can be made. In lines 3 and 4, sets  $X_1$  and  $X_2$  are computed for one net n. In the worst case all components  $\mathcal{D} \cup \mathcal{B}$  are connected to n. This computation can be made fast by using an appropriate index, that is based on red–black trees (Sedgewick 1988), yielding logarithmic complexity for the worst–case runtimes  $t_3^{\text{max}}$  and  $t_4^{\text{max}}$ ,

$$t_3^{\text{max}} = t_4^{\text{max}} \in \mathcal{O}(\log|\mathcal{D} \cup \mathcal{B}|) ,$$

(3.15)

In line 5, every new pair requires one insert operation into set X. Assuming that X is implemented using red-black trees and  $|X_1| = |X_2| = |\mathcal{D} \cup \mathcal{B}|$  in the worst case (Sedgewick 1988), this yields,

$$t_5^{\text{max}} \in \mathcal{O}(|\mathcal{D} \cup \mathcal{B}|^2 \log|\mathcal{D} \cup \mathcal{B}|^2) = \mathcal{O}(|\mathcal{D} \cup \mathcal{B}|^2 \log|\mathcal{D} \cup \mathcal{B}|)$$

. (3.16)

Thus, the worst–case runtime  $t_{2-5}$  for the upper loop is,

$$t_{2-5}^{\max} = |\mathcal{N}|(t_3^{\max} + t_4^{\max} + t_5^{\max}) \in \mathcal{O}(|\mathcal{N}| \cdot |\mathcal{D} \cup \mathcal{B}|^2 \cdot \log|\mathcal{D} \cup \mathcal{B}|). \tag{3.17}$$

The lower loop is executed |X| times, which is  $|\mathcal{D} \cup \mathcal{B}|^2$  in the worst case. In addition, it must be assumed that  $r_{12,t}$  is true for every pair and consequently  $|\mathcal{D} \cup \mathcal{B}|^2$  new pairs are created, i.e.,

$$|B|_{\text{findPairs}}^{\text{max}} = |\mathcal{D} \cup \mathcal{B}|^2$$

(3.18)

Creating a new pair has logarithmic complexity with respect to the overall number of components, since the index mentioned above must be updated. Overall, the complexity for the worst–case runtime  $t_{6-7}^{\max}$  for lines 6 and 7 is,

$$t_{6-7}^{\max} \in \mathcal{O}(|\mathcal{D} \cup \mathcal{B}|^2 \log|\mathcal{D} \cup \mathcal{B}|)$$

(3.19)

The runtime complexity for the upper loop is dominant, yielding the following complexity for the worst–case runtime  $t_{\text{findPairs}}^{\text{max}}$  of the complete function,

$$t_{\text{findPairs}}^{\text{max}} \in \mathcal{O}(|\mathcal{N}| \cdot |\mathcal{D} \cup \mathcal{B}|^2 \cdot \log|\mathcal{D} \cup \mathcal{B}|)$$

(3.20)

However, these assumptions are hardly realistic. In a real circuit, there are many nets with only few devices connected. In addition, it can be assumed, that  $r_{1,t}$  and  $r_{2,t}$  are only true for a number of devices that is approximately constant. This yields the following typical runtime complexity  $t_{2-5}^{\text{typ}}$  of the upper loop,

$$t_{2-5}^{\text{typ}} \in |\mathcal{N}| \cdot (\mathcal{O}(1) + \mathcal{O}(1) + \mathcal{O}(\log|\mathcal{D} \cup \mathcal{B}|) = \mathcal{O}(|\mathcal{N}| \cdot \log|\mathcal{D} \cup \mathcal{B}|) \tag{3.21}$$

Experiments show that the number of created new pairs |B| is approximately linear to the circuit size,

$$|B|^{\text{typ}} \in \mathcal{O}(|\mathcal{D} \cup \mathcal{B}|)$$

(3.22)

Consequently the typical runtime  $t_{6-7}^{\text{typ}}$  has the following complexity,

$$t_{6-7}^{\text{typ}} \in \mathcal{O}(|\mathcal{D} \cup \mathcal{B}| \log|\mathcal{D} \cup \mathcal{B}|),$$

(3.23)

yielding the following typical runtime complexity for the function,

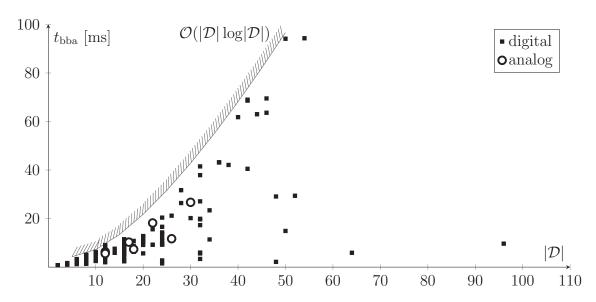

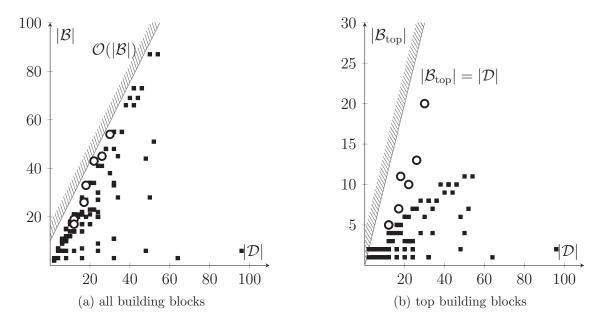

$$t_{\text{findPairs}}^{\text{typ}} \in \mathcal{O}\left(\left(\left|\mathcal{N}\right| + \left|\mathcal{D} \cup \mathcal{B}\right|\right) \log \left|\mathcal{D} \cup \mathcal{B}\right|\right).$$

(3.24)

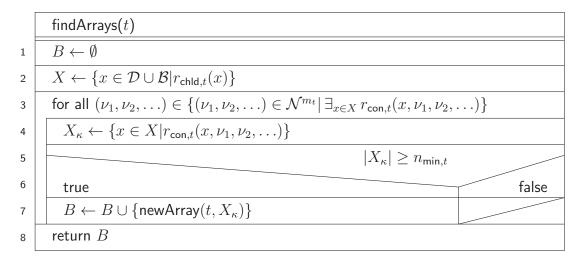

### 3.2.2. Recognition of Arrays

Next, the algorithm to find arrays is discussed. Theoretically, an array of type t can be found by evaluating a rule function  $\rho_t(x_1, x_2, \ldots, x_n)$  for n-tuples  $(x_1, x_2, \ldots, x_n)$  of potential children as follows,

$$\rho_t(x_1, x_2, \dots, x_n) \Leftrightarrow n \geq n_{\min,t} \wedge \bigvee_{i \in \{1, 2, \dots, n\}} r_{\text{chld}}(x_i) \wedge \bigvee_{\nu_1, \nu_2, \dots, \nu_{m_t} \in \mathcal{N}} \bigvee_{i \in \{1, 2, \dots, n\}} r_{\text{con},t}(x_i, \nu_1, \nu_2, \dots, \nu_{m_t}) . \quad (3.25)$$

Constant  $n_{\min,t}$  is the minimum number of components for an array of type t. Function

$$r_{\text{chld}}: \mathcal{D} \cup \mathcal{B} \to \mathbb{B},$$

(3.26)

describes the properties of each child. It can contain conditions about type, subtype, existence of parents as wells as required and forbidden connections of the child with itself. Function,

$$r_{\text{con}}: (\mathcal{D} \cup \mathcal{B}) \times \mathcal{N}^{m_t} \to \mathbb{B}$$

(3.27)

describes the connectivity between the children and does only contain conditions about required connections. The size  $m_t$  of the tuple of nets  $\nu_1, \nu_2, \dots, \nu_{m_t}$  is type specific and constant.

In addition, the tuple must be the largest possible one. This means, it must not be possible to extend a valid tuple  $(x_1, x_2, \ldots, x_n)$  by a child  $x_{n+1}$ , such that  $\rho_t$  is still valid, i.e.,

$$\frac{\exists}{x_{n+1}} \rho_t(x_1, x_2, \dots, x_n, x_{n+1}) . \tag{3.28}$$

Based on Eq. (3.25), Eq. (3.28) can be rewritten to,

$$\frac{\exists}{x_{n+1}} \left[ n+1 \ge n_{\min,t} \wedge \bigvee_{i \in \{1,2,\dots,n+1\}} r_{\operatorname{cohd}}(x_i) \right]$$

$$\wedge \underbrace{\exists}_{\nu_1,\nu_2,\dots,\nu_{m_t} \in \mathcal{N}} \bigvee_{i \in \{1,2,\dots,n+1\}} r_{\operatorname{con},t}(x_i,\nu_1,\nu_2,\dots,\nu_{m_t}) \right]$$

$$\Leftrightarrow \underbrace{\exists}_{x_{n+1}} \left[ \underbrace{n+1 \ge n_{\min,t}}_{1 \text{ if } \rho_t(x_1,x_2,\dots,x_n)=1} \wedge \bigvee_{i \in \{1,2,\dots,n\}} r_{\operatorname{chld}}(x_i) \wedge r_{\operatorname{chld}}(x_{n+1}) \right]$$

$$\wedge \underbrace{\exists}_{\nu_1,\nu_2,\dots,\nu_{m_t} \in \mathcal{N}} \bigvee_{i \in \{1,2,\dots,n+1\}} r_{\operatorname{con},t}(x_i,\nu_1,\nu_2,\dots,\nu_{m_t}) \right]$$

(3.29)

Under the assumption that  $\rho_t(x_1, x_2, \dots, x_n) = 1$  the first and second term are always true. This yields,

$$\frac{\exists}{x_{n+1}} \left[ r_{\text{chld}}(x_{n+1}) \wedge \underbrace{\exists}_{\nu_1,\nu_2,\dots,\nu_{m_t} \in \mathcal{N}} \underbrace{\forall}_{i \in \{1,2,\dots,n+1\}} r_{\text{con},t}(x_i,\nu_1,\nu_2,\dots,\nu_{m_t}) \right] .$$

(3.30)

This means, there may be no child  $x_{n+1}$  that fulfills  $r_{\text{chld},t}$  and is connected in parallel.

For example, for a normal transistor array the rule functions and type-specific con-

stants are,

$$n_{\min,\text{nta}} = 1 \tag{3.31}$$

$$m_{\rm nta} = 3 \tag{3.32}$$

$$r_{\text{chld,nta}}(x) \Leftrightarrow \underbrace{\left(x.type = \text{trans}\right)}_{\text{type}} \land \underbrace{\left(x.net(\text{gt}) \neq x.net(\text{dn})\right)}_{\text{forbidden connection}}$$

$$\wedge \underbrace{\left(x.net(gt) \neq x.net(sc)\right) \wedge \left(x.net(sc) \neq x.net(dn)\right)}_{}$$

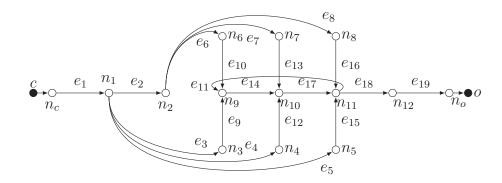

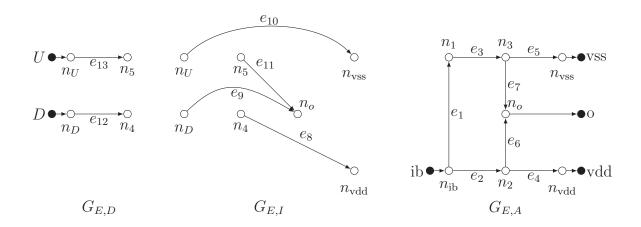

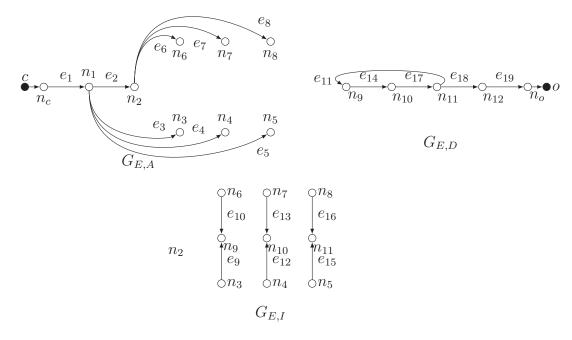

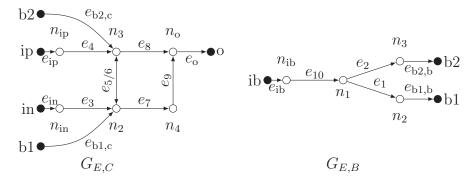

(3.33)

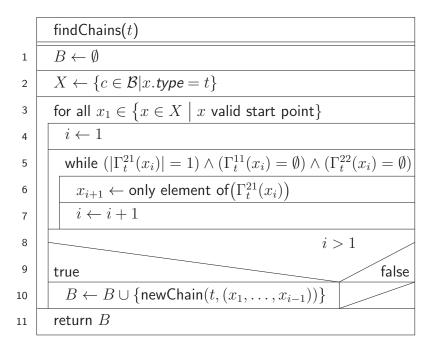

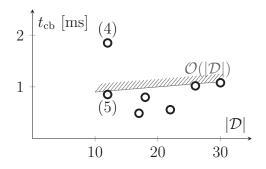

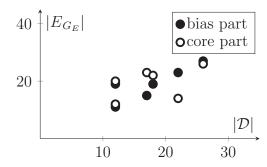

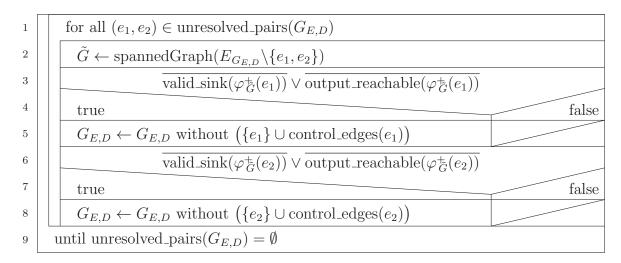

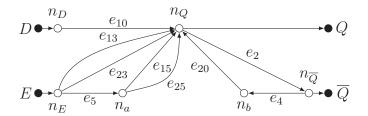

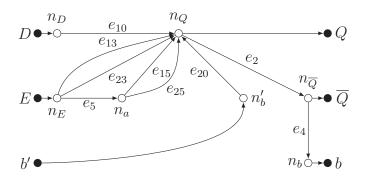

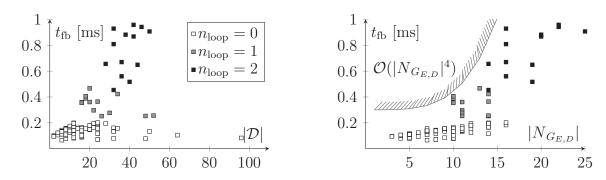

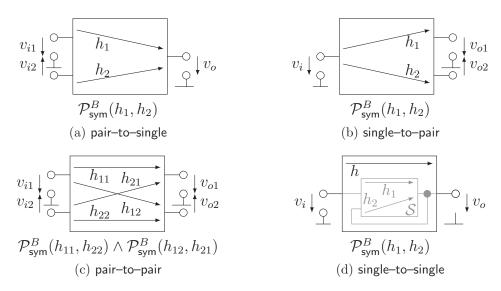

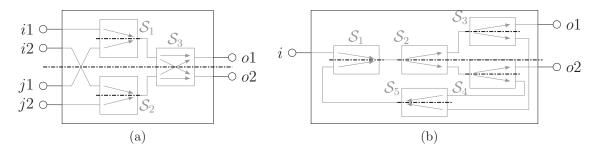

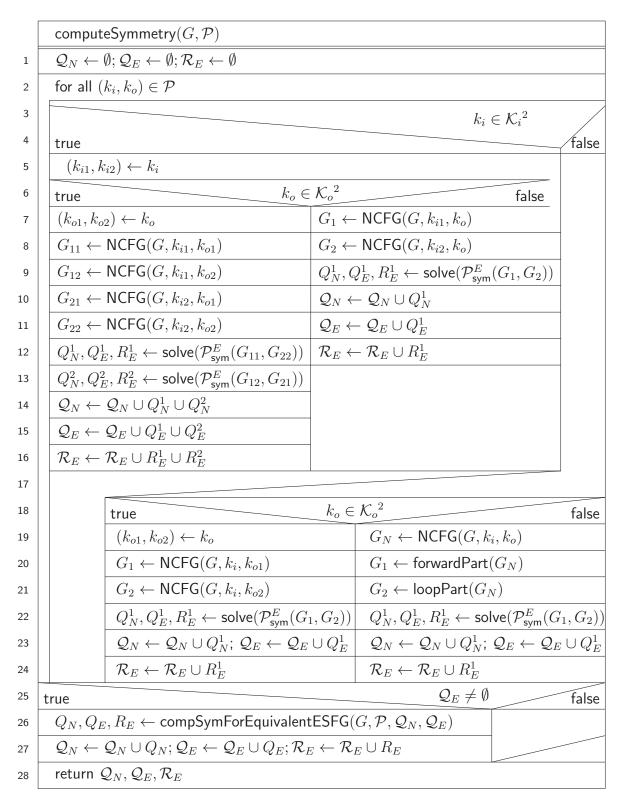

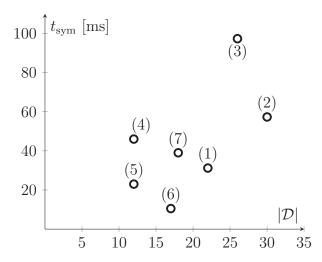

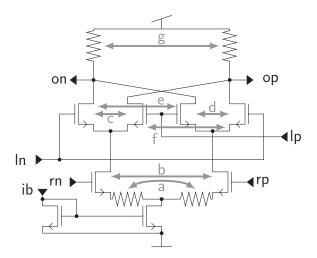

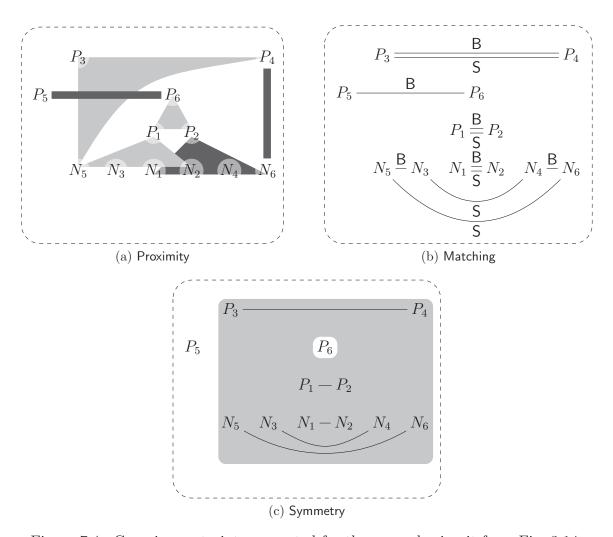

$$r_{\text{chld,nta}}(x) \Leftrightarrow \underbrace{\left(x.type = \text{trans}\right)}_{\text{type}} \wedge \underbrace{\left(x.net(\text{gt}) \neq x.net(\text{dn})\right)}_{\text{forbidden connection}} \wedge \underbrace{\left(x.net(\text{gt}) \neq x.net(\text{sc})\right) \wedge \left(x.net(\text{sc}) \neq x.net(\text{dn})\right)}_{\text{forbidden connections}}$$