# Introduction to Microprocessors DCAP210

Edited by: Gurwinder Kaur

# INTRODUCTION TO MICROPROCESSORS

Edited By: Gurwinder Kaur

Printed by EXCEL BOOKS PRIVATE LIMITED A-45, Naraina, Phase-I, New Delhi-110028 for Lovely Professional University Phagwara

# SYLLABUS

# Introduction to Microprocessors

*Objectives:* To develop the hardware skills required for the complete understanding of the architecture and programming of the microprocessor used in computing world.

| S. No. | Description                                                                                                                                                       |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.     | Microprocessors, Microcomputers, and Assembly Language: Microprocessors, microprocessor Instruction Set and Computer Languages, Application                       |  |  |

| 2.     | <b>Introduction to 8085 Assembly Language Programming:</b> 8085 programming model, Instruction Classification, How to write a simple program?                     |  |  |

| 3.     | <b>Microprocessor Architecture and Microcomputer Systems:</b> Microprocessor architecture and its operation, Memory, I/O devices, Example of Microcomputer system |  |  |

| 4.     | <b>8085 Microprocessor Architecture and Memory Interfacing:</b> 8085 MPU, Memory Interfacing, How does an 8085-Based Single board Microcomputer work?             |  |  |

| 5.     | <b>Interfacing I/O Devices:</b> Basic interfacing Concepts, Interfacing output displays, Interfacing input devices, Memory Mapped I/O                             |  |  |

| 6.     | Introduction to 8085 Instructions: Data transfer operations, Arithmetic operations, Logic operations, branch operations                                           |  |  |

| 7.     | <b>Programming Techniques with Additional Instructions:</b> Programming techniques: Looping, Counting and Indexing, Additional Data transfer instructions         |  |  |

| 8.     | Counters and Time delays: Counter and time delays, Illustrative program: Hexadecimal counter                                                                      |  |  |

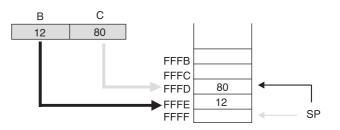

| 9.     | Stack and Subroutines: Stack, Subroutine, Restart, Conditional call and Return Instruction                                                                        |  |  |

| 10.    | Interrupts: 8085 interrupts                                                                                                                                       |  |  |

# CONTENT

| Unit 1:  | Microprocessors and Microcomputers                  | 1   |

|----------|-----------------------------------------------------|-----|

|          | Gurwinder Kaur, Lovely Professional University      |     |

| Unit 2:  | Introduction to Assembly Language                   | 20  |

|          | Gurwinder Kaur, Lovely Professional University      |     |

| Unit 3:  | Assembly Language Programming of 8085               | 34  |

|          | Gurwinder Kaur, Lovely Professional University      |     |

| Unit 4:  | Microprocessor Architecture                         | 53  |

|          | Dinesh Kumar, Lovely Professional University        |     |

| Unit 5:  | Microcomputer System                                | 67  |

|          | Dinesh Kumar, Lovely Professional University        |     |

| Unit 6:  | The 8085 Microprocessor Architecture                | 77  |

|          | Dinesh Kumar, Lovely Professional University        |     |

| Unit 7:  | Memory Interfacing                                  | 97  |

|          | Parminder Kaur, Lovely Professional University      |     |

| Unit 8:  | Interfacing I/O Devices                             | 110 |

|          | Parminder Kaur, Lovely Professional University      |     |

| Unit 9:  | Introduction to 8085 Instructions                   | 125 |

|          | Parminder Kaur, Lovely Professional University      |     |

| Unit 10: | Programming Techniques with Additional Instructions | 137 |

|          | Gurwinder Kaur, Lovely Professional University      |     |

| Unit 11: | Counters and Time Delays                            | 152 |

|          | Gurwinder Kaur, Lovely Professional University      |     |

| Unit 12: | The Stacks                                          | 166 |

|          | Dinesh Kumar, Lovely Professional University        |     |

| Unit 13: | Subroutines                                         | 176 |

|          | Dinesh Kumar, Lovely Professional University        |     |

| Unit 14: | Interrupts                                          | 185 |

|          | Gurwinder Kaur, Lovely Professional University      |     |

# Unit 1: Microprocessors and Microcomputers

Notes

| CONTEN      | ITS                                |

|-------------|------------------------------------|

| Objectives  |                                    |

| Introductio | n                                  |

| 1.1 Micro   | processor                          |

| 1.2 Micro   | computer                           |

| 1.2.1       | Automobile Analogy                 |

| 1.2.2       | Intel MCS-4 4-B Chip Set           |

| 1.2.3       | Intel 8008 Microprocessor          |

| 1.2.4       | 8080 More and No More              |

| 1.3 Histor  | rical Perspective                  |

| 1.3.1       | Moore's Law                        |

| 1.4 Micro   | processor Instruction Set          |

| 1.4.1       | Implied Addressing                 |

| 1.4.2       | Register Addressing                |

| 1.4.3       | Immediate Addressing               |

| 1.4.4       | Direct Addressing                  |

| 1.4.5       | Register Indirect Addressing       |

| 1.4.6       | Combined Addressing Modes          |

| 1.4.7       | Timing Effects of Addressing Modes |

| 1.4.8       | Decoding                           |

| 1.5 Sumn    | nary                               |

| 1.6 Keyw    | ords                               |

| 1.7 Self-A  | Assessment Questions               |

| 1.8 Revie   | w Questions                        |

| 1.9 Furth   | er Reading                         |

|             |                                    |

# Objectives

After studying this unit, you will able to understand the following:

- Explain about microprocessor

- Describe the important areas of microprocessor

- Explain about microcomputer

- Understand the microprocessor instruction set

#### Introduction

A microprocessor, sometimes called a logic chip, is a computer processor on a microchip.

The microprocessor contains all, or most of, the central processing unit (CPU) functions and is the "engine" that goes into motion when you turn your computer on. A microprocessor is designed to perform arithmetic and logic operations that make use of small number-holding areas called registers. Typical microprocessor operations include adding, subtracting, comparing two numbers, and fetching numbers from one area to another. These operations are the result of a set of instructions that are part of the microprocessor design.

When your computer is turned on, the microprocessor gets the first instruction from the basic input/output system (BIOS) that comes with the computer as part of its memory. After that, either the BIOS, or the operating system that BIOS loads into computer memory, or an application program is "driving" the microprocessor, giving it instructions to perform.

# 1.1 Microprocessor

Microprocessors are regarded as one of the most important devices in our everyday machines called computers. Before we start, we need to understand what exactly microprocessors are and their appropriate implementations. Microprocessor is an electronic circuit that functions as the central processing unit (CPU) of a computer, providing computational control. Microprocessors are also used in other advanced electronic systems, such as computer printers, automobiles, and jet airliners. Typical microprocessors incorporate arithmetic and logic functional units as well as the associated control logic, instruction processing circuitry, and a portion of the memory hierarchy. Portions of the interface logic for the input/output (I/O) and memory subsystems may also be infused, allowing cheaper overall systems. While many microprocessors have single chip designs, some high-performance designs rely on a few chips to provide multiple functional units and relatively large caches.

When combined with other integrated circuits that provide storage for data and programs, often on a single semiconductor base to form a chip, the microprocessor becomes the heart of a small computer, or microcomputer. Microprocessors are classified by the semiconductor technology of their design (TTL, transistor-transistor logic; CMOS, complementary-metal-oxide semiconductor; or ECL, emitter-coupled logic), by the width of the data format (4-bit, 8-bit, 16-bit, 32-bit, or 64bit) they process; and by their instruction set (CISC, complex-instruction-set computer, or RISC, reduced instruction set computer: see RISC processor). TTL technology is most commonly used, while CMOS is favoured for portable computers and other battery-powered devices because of its low power consumption. ECL is used where the need for its greater speed offsets the fact that

it consumes the most power. Four-bit devices, while inexpensive, are good only for simple control applications; in general, the wider the data format, the faster and more expensive the device. CISC processors, which have 70 to several hundred instructions, are easier to program than RISC processors, but are slower and more expensive.

Microprocessors have been described in many different ways. They have been compared with the brain and the heart of humans. Their operation has been likened to a switched board, and to the nervous system in an animal. They have often been called microcomputers. The original purpose of the microprocessor was to control memory. That is what they were originally designed to do, and that is what they do today. Specifically, a microprocessor is "a component that implements memory."

A microprocessor can do any information-processing task that can be expressed, precisely, as a plan. It is totally uncommitted as to what its plan will be. It is a truly general-purpose information processing for microprocessor.

Computer's performance is also influenced by the system bus architecture, memory used, type of the processor and software program being running. Pentium 4 is the fastest type of the Intel's processor that contains 125,000,000 transistors and operates at the speed of 3.6 GHz.

# **1.2 Microcomputer**

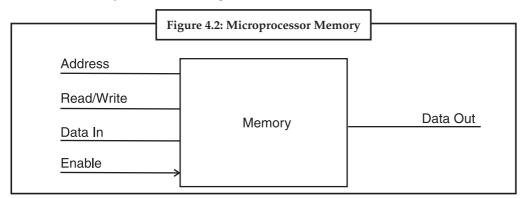

The term microcomputer is generally synonymous with personal computer, or a computer that depends on a microprocessor. Microcomputers are designed to be used by individuals, whether in the form of PCs, workstations or notebook computers. A microcomputer contains a CPU on a microchip (the microprocessor), a memory system (typically ROM and RAM), a bus system and I/O ports, typically housed in a motherboard.

Intel's first microcomputer appeared in November 1971:

Intel delivered two different microcomputers five months apart: the MCS-4, emphasizing low cost in November 1971, and the MCS-8, for versatility in April 1972. "The MCS-4 and MCS-8 CPU chip sell in quantity for less than ₹ 1000 each, and are powerful alternatives to random logic". These two Microcomputer Systems (MCS) were aimed at two very different markets. One would eventually lead to the under ₹ 4500 controller, the other would be the engine for a versatile personal computer (PC). By analogy it was like creating the "motorbike" and the "station wagon" at the same time. The advertised prophecy of "a new era" became fulfilled over the subsequent 20-year period.

# 1.2.1 Automobile Analogy

Our challenge was how to scale down a general purpose computer to fit on to a chip. Imagine that the only passenger vehicle in existence is an eight-passenger van costing ₹ 2250 000. At first it would be difficult to imagine ₹ 1000 version of this vehicle. The specifications would need to be drastically reduced to meet the price goal. Some ideas to consider:

- 1. reducing capacity by 75%

- 2. reducing speed by 90%

- 3. reducing range by 75%

The golf cart might be the result. However, if golf carts are unknown at the time, it is not easy to envision how to scale down a van.

## 1.2.2 Intel MCS-4 4-B Chip Set

Although Intel began as a memory chip company, in 1969 we took on a project for Busicom of Japan to design eight custom LSI chips for a desktop calculator. Each custom chip had a specialized

function—keyboard, printer, display, serial arithmetic, control, etc. With only two designers, Intel didn't have the manpower to do that many custom chips. We needed to solve their problems with fewer chip designs. Ted Hoff chose a programmed computer solution using only one complex logic chip (CPU) and two memory chips; memory chips are repetitive and easier to design. Intel was a memory chip company, so we found a way to solve our problem using memory chips!

In 1970 Intel designers implemented a 4-b computer on three LSI chips (CPU, ROM, RAM) housed in 16-pin packages. Reducing the data word to 4-b (for a BCD digit) was a compromise between 1-b serial calculator chips and conventional 16-b computers.

The scaled down 4-b word size made the CPU chip size practical (2200 transistors). We used the 16-pin package, because it was the *only one* available in our company. This limited pin count forced us to time multiplex a 4-b bus. This small bus simplified the printed circuit board (PCB), as it used fewer connections. However, the multiplex logic increased chip area of the specialized ROM/RAM memory chips, which then had to have built-in address registers. Increasing the transistor count to save chip connections was a novel idea. In school we learned to minimize logic, not interconnections! Later, LSI "philosophers" would preach, "logic is free".

|               | 1. MCS-4 Features:                                                                                                                             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 256 × 8       | Read Only Memory (2 kb ROM) with 4-b I/O port                                                                                                  |

| $80 \times 4$ | Random Access Memory (320 b RAM) with 4-b output port                                                                                          |

| 4-b           | CPU chip with: 16 x 4-b index registers, 45 1 and 2 byte instructions, 4-level Subroutine Address Stack, 12-b Program Counter (4 k addresses). |

#### (A) ROM Chip (4001)

Conventional calculators utilized specialized custom chips for keyboard, display, and printer control. With the MCS-4 all control logic is done in firmware, program stored in ROM. A single ROM chip design is customized (with a mask during chip manufacturing) for a customer's

particular program. The CPU's 12-b Program Counter addresses up to 16 ROM chips. Simple applications use only one ROM chip; the desktop calculator used four. The same chip mask also configured each ROM port bit as an input or output.

Additionally, the ROM chip had an integrated address register, an output data register, multiplexors, and control and timing logic. The specialized RAM chip had similar resources.

### (B) RAM Chip (4002)

Calculators need to hold several 16-digit decimal floating-point numbers. We organized the RAM accordingly, and ended up with a 20-digit word (80 b):

16 digits for the fraction

2 digits for the exponent

2 digits for signs and control

$20 \text{ digits} \times 4 \text{ b/digit}$

The RAM chip stored four 80-b numbers and additionally the chip had an output port. The use of three-transistor dynamic memory cells made the RAM chip feasible. A built-in refresh counter was used to maintain data integrity. Refresh took place during instruction fetch cycles, when the RAM data was not being accessed. Dynamic RAM memory cells were also used inside the CPU for the 64-b index register array and 48-b Program Counter/stack array. Intel expertise in dynamic memory was an enabling factor for the MCS-4!

#### (C) Input/Output Ports

To conserve chip count and to utilize existing power/clock pins, the 16-pin ROM and RAM chips also had integrated 4-b ports for direct connection of I/O devices. To activate an output, a program selected a particular RAM/ROM chip (using an index register) and sent 4-b of accumulator data from the CPU to the selected output port. In the desk calculator application, the display, keyboard, and printer were connected to these ports. Keyboard scanning, decoding, and debouncing were all done under program control of the I/O ports; all printer and display refresh was done in firmware. A small shift register (4003) was used for output port expansion. External transistors and diodes were used for amplification and isolation.

#### (D) Microprocessor — CPU Chip (4004)

In the calculator application, each user key stroke caused thousands of CPU instructions to be executed from ROM. We wrote many subroutines which operated on 16-digit numbers stored in RAM.

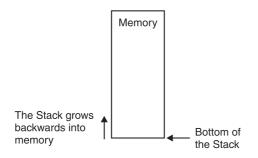

As an example, a 10-byte loop for digit serial addition took about 80  $\mu$ s/digit (similar speed as IBM 1620 computer sold in 1960 for ₹ 100 000). In this add routine a CPU index register would address each of the 16 digits stored in the RAM memory. The program would bring in one digit at a time into the CPU's accumulator register to do arithmetic. A Decrement and Jump instruction was used to index to the next RAM location. One major difference, compared to most computers, was the MCS-4's separate program and data memories. Conventional computers ran programs from RAM (core) memory. However, our application firmware needed to be permanently stored in ROM. A major change was needed for subroutine linkage. Normally, as part of a minicomputer subroutine call instruction execution (PDP-8, HP 2114) the calling program's return address would be saved at the top of the subroutine in RAM. Since MCS-4 routines were in ROM (can't write into it) we could not use this method. Instead. We used, a push down stack inside the CPU for saving up to three return addresses. This was not a new idea. Stacks had been used in Burrough's computers and the IBM 1620, which Ted Hoff had programmed—we used our experience with large-scale computers. Ultimately this limited depth of four levels (which was all we could squeeze on to this small chip) was frustrating for programmers and succeeding generations went to eight or more levels (8008, 4040, 8048). Today's computers have stacks of many megabytes; but their usage is very similar to their use in the 4004.

#### (E) Distributed Logic Architecture

The time division multiplexing of the 4-b bus, the on-chip dynamic RAM memories, and the CPU's address stack are the highlights of the MCS-4 architecture. However, there is another interesting feature—distributed decoding of instructions. The ROM/RAM chips watched the bus, and locally decoded port instructions, as they were sent from the ROM. This eliminated the need for the CPU to have separate signal lines to the I/O ports, and also saved CPU logic. This is not a feature used in conventional computers.

#### (F) MCS-4 Applications

The smallest system would contain two chips a CPU and a ROM. A typical calculator had 4 ROM's and a RAM chip with five I/O ports, (20) wires for connecting peripheral devices. A fully loaded system could have 16 ROM and 16 RAM chips, and obviously a plethora of I/O ports. Typical applications included:

| digital scales      | taxi meters      |  |

|---------------------|------------------|--|

| gas pumps           | traffic light    |  |

| elevator control    | vending machines |  |

| medical instruments |                  |  |

Notes

Busicom of Japan produced several calculator models using the MCS-4 chip set. Ted Hoff made the original proposal for the MCS-4 and did the feasibility study for the first calculator. Federico Faggin did all of the logic and circuit design and implemented the layout; Busicom's M. Shima wrote most of Busicom's firmware. The Intel patent on the MCS-4 has 17 claims, but the single chip processor is not claimed as an invention.

Intel supported the MCS-4 with a Cross assembler and later with a standalone development system, the Intellec "blue" box.

The MCS-4 evolved into the single chip microcomputers 8048/8051. These chips emphasized small size and low cost. These, along with a variety of other manufacturer's parts, have evolved into the under 1 computer on a chip used in toys, automobiles, and appliances. These chips are very pervasive—almost invisible.

# 1.2.3 Intel 8008 Microprocessor

Intel made a custom 512-b shift register memory chip for use in (their customer) Data point's low cost bit-serial computer. This 8-b CPU, implemented with TTL MSI, had around 50 data processing instructions.

This custom chip design was never used by Data point, and it became a standard Intel product, which marketing dubbed the 8008 (twice 4004!).

Although the arithmetic unit and registers were twice as large as in the MCS-4, we expected that the control logic could be about the same if we deleted a few Data point defined instructions. Unlike the MCS-4's two-memory address space, the 8008 had one memory address space for program and data. The symmetric and regular instruction set was attractive. However, the only memory addressing was indirect through the High-Low (HL) register pair. Today's computers have huge amounts of memory, and a plethora of memory addressing instructions.

The 8008 CPU had six 8-b general purpose registers (B, C, D, E, H, L) and an 8-b accumulator. The push down program counter stack had 8-levels. Both of these register arrays were implemented with dynamic memory cells and the CPU had built-in "hidden" refresh during instruction fetch cycles, similar to the MCS-4.

We decided that the 8008 would utilize standard memory components (not custom ROM's and RAM's as in the MCS-4). This increased the parts count on a minimum system because separate

address registers, multiplexors and I/0 latch chips would need to be added to make the system work; in practice about 40 additional small chips were needed. But standard memories were available in high volume at low cost, and in a larger system the extra chip overhead could be tolerated. Using memory chips with different access times requires a synchronizer scheme, and therefore ready/wait signal pins were provided to perform a handshake function. These interface signals are more sophisticated in today's processors, but the 8008 demonstrated the idea.

The availability of Electrically Programmed ROM's (EPROM) was significant in allowing customers to experiment with their software. A product synergy evolved between Intel's memory component business and the microprocessor. Intel had an 18-pin package in volume production for the 1k dynamic RAM chip (1103); this gave two more pins for the 8008 than we had on the MCS-4, but we still had to time-multiplex an 8-b bus. By reducing the Program Counter width to 14-b we saved two package pins. The jump instruction contained a 16-b address, but two of the bits were ignored. The 8008 could have 16k bytes of memory, and at the time, this seemed enormous. (Today, users want 16 meg.)

#### (A) Little Endian

Some have wondered why the addresses in the 8008 were stored "backward" with the little end first, e.g. the low order byte of a two-byte address is stored in the lower addressed memory location. We (regrettably) specified this ordering as part of the JUMP instruction format in the spirit of compatibility with the Data point 2200. Recall that their original processor was bit serial; the addresses would be stored low to high bit in the machine code (bit-backward). Other computer makers organize the addresses with the "big end" first. The lack of standardization has been a problem in the industry.

#### (B) Applications

One of the first users of the 8008 was Seiko in Japan for a sophisticated scientific calculator. Other users included business machines and a variety of general purpose computers.

Intel did not apply for a patent on the 8008. Data point contracted with Texas Instruments in 1970 to get a second source for this chip. TI patented their design, but never got into production.

After about one year of experience with programming the 8008 CPU chip, we had a number of requested enhancements from our users. We proposed to build the 8080 as a follow on chip; this chip was very popular and led to the microcomputer revolution and the Personal Computer. It is ironic that Data point ultimately competed in the marketplace with PC products based upon their own, Data point defined, architecture!

#### 1.2.4 8080 More and No More

#### (A) More

Based upon Intel's success with their new microcomputer product line Faggin convinced Vasdasz in 1972 to fund a project to convert the P-MOS 8008 into the newer N-MOS technology. This technology offered about a 2x speedup without making logic changes. After a short study, it was determined that a new mask set was needed because of the incompatibility of transistor size ratios. Faggin reckoned that since a new mask set was needed, he would fix some of the 8008's shortcomings.

We evolved the 8080 specification to improve performance 10x. We used the greater density to put in more logic (4500 transistors) and do more in parallel; the on chip control logic grew by 50%.

We put the stack in memory, did 16-b operations, and improved memory addressing. Now 40pin plastic packages were available, and the address bus and data bus could be brought out in parallel. This design also simplified the external circuitry and TTL voltage compatible signals were provided.

Deleting the on-chip stack saved chip area, but was a net advantage to the user—now the stack had unlimited size. In the 8080, the registers were arranged as pairs of 8 b, to provide 16-b data handling. The three register pairs were designated as: BC, DE, HL. The High/Low register pair was the only way to address memory in the older 8008. This was limiting to programmers, so in the 8080 direct memory addressing instructions were added, as well as several specialized instructions for the HL register pair. One instruction, XTHL, provided for exchanging the top of stack with HL; another instruction, XHLD, swapped the contents of HL with the DE register pair. As these special instructions were not very symmetric, applying only to HL, we optimized their logic implementation. One of Ted Hoff's tricks was the use of an *exchange* flip-flop for DE/HL. This flip-flop designated one of the pairs as HL and the other register pair as DE. Simply toggling this flip-flop affected an apparent exchange! This saved a lot of logic; but by mistake, the reset pin had been connected to this flip-flop. An early 8080 user manual stated: "after reset, the HL/DE register contents may be exchanged" (later the reset connection was cut). The lack of instruction set symmetry was a nuisance to programmers and later CPU's instruction sets were considerably more regular; of course there were more transistors "to bum."

#### (B) No More

This is why the last 12 instructions were never implemented and why there was room in the instructions set for the 8085 microprocessor's added instructions. The 8080 was very successful in the market. Meanwhile, competition blossomed and a variety of great processors developed including the Motorola 6800 and the MOS Technology 6502. The 8080 CPU chip was patented by Intel and has three claims.

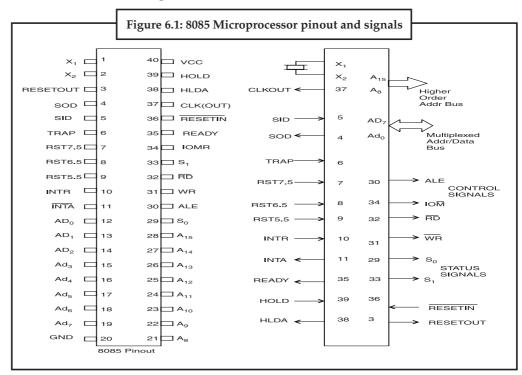

#### (C) 8085

To meet competition in 1976, Intel decided to develop a more integrated version of the 8080. This chip contained 6500 transistors. The new N-MOS was more TTL compatible and this chip needed few external parts.

There were 12 unused operation codes in the 8080 which provided room to expand the CPU's function. At Intel, a committee studied, argued, and finally decided after many months which instructions to add. Although all of these new codes were utilized by the 8085 designers, by the time this product got to market it was almost obsolete. To reduce compatibility requirements with the 8086 which was in design, 10 of the new 12 instructions were never announced in the data sheet. They have only been an interesting historical anomaly and a lesson about design by committee.

#### (D) 8086

In 1978, Intel's W. Davidow, vice president of the microcomputer group, rushed to staff a 16 b microcomputer development project. It was to have around 30 000 transistors, 12 times more than the 4004.

This new computer had multiplication and division and a host of other new features. However, it was constrained to be upwardly compatible with the 8080 (and 8008). Accordingly, the designers decided to keep the 16 b basic addresses and to use segment registers to get extended 20 b addresses. Two versions were created—the 8088 had an 8-b data bus for compatibility with 8-b memory systems, and the 16 b 8086. With 1 megabyte of memory addressing, this processor was a serious contender in the computer market place. This chip density required to match the 16-b minicomputers was "arriving" as had been predicted.

The decision by IBM to use the 8088 in a word processor and personal computer created enormous market momentum for Intel. The 186, 286, 386, 486 followed over the next 15 years, with some shadow of 8008 features still apparent. These components would be "truly pervasive".

## **1.3 Historical Perspective**

The promises of high density solid state circuitry were becoming apparent in the 1950's. In 1959, Holland contemplated large-scale computers built with densities of 108 components per cubic foot. The integrated circuit was developed in parallel at both TI and Fairchild; the density of IC's was doubling every year. "Entire subsystems on a chip" were predicted if a high volume standard chip could be defined. For a 1966 forecast of chip complexity, it was then estimated that about 10 k-20 k gates would fit on a chip and that a good portion of a CPU would therefore be on one chip.

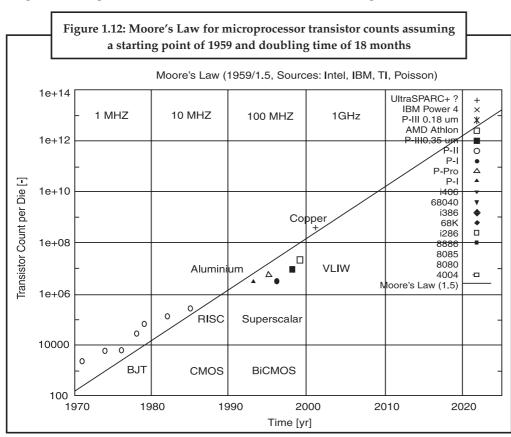

#### 1.3.1 Moore's Law

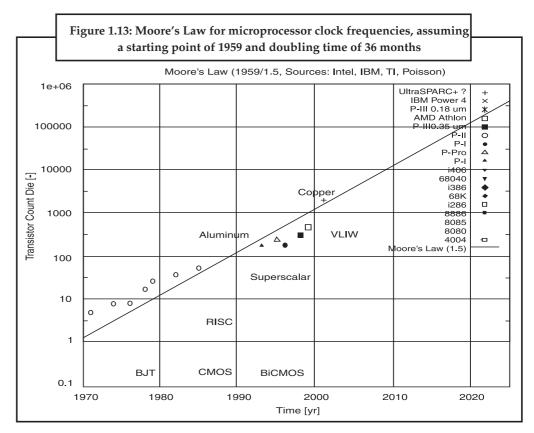

Gordon Moore's empirical relationship is cited in a number of forms, but its essential thesis is that the numbers of transistors which can be manufactured on a single die will double every 18 months. The starting point for this exponential growth curve is usually set at 1959 or 1962, the period during which the first silicon planar transistors were designed and tested.

We now have four decades of empirical data to validate Moore's argument. Figure 1.12 depicts a sampling of microprocessor transistor counts, against the basic form of Moore's Law. Clearly the empirical data supports the argument well, even allowing for considerable noise in the dataset.

Similar plots for high density Dynamic Random Access Memory (DRAM) devices yield a very similar correlation between Moore's Law and actual device storage capacity.

Two important questions can be raised. The first is that of "how do we relate the achievable computing performance of systems to Moore's Law?". The second is the critical question of "how long will Moore's Law hold out?". Both deserve careful examination.

The computing performance of a computer system cannot be easily measured, nor can it be related in a simple manner to the number of transistors in the processor itself. Indeed, the only widely used measures of performance are various benchmark programs, which serve to provide essentially ordinal comparisons of relative performance for complete systems running a specific benchmark. This is for good reasons, since the speed with which any machine can solve a given problem depends upon the internal architecture of the system, the internal micro architecture of the processor chip itself, the internal bandwidth of the buses, the speed and size of the main

memory, the performance of the disks, the behaviour of the operating system software and the characteristics of the compiler used to generate executable code. The clock speed of the processor chip itself is vital, but in many instances may be less relevant than the aggregated performance effects of other parts of the system.

What can be said is that machines designed with similar internal architectures, using similar operating systems, compilers and running the same compute bound application, will mostly yield benchmark results in the ratios of their respective clock speeds. For instance, a compute bound numerically intensive network simulation written by the author was run on three different generations of Pentium processor, and a mid 1990s SuperSPARC, all running different variants of UNIX, but using the same GCC compiler. The time taken to compute the simulation scaled, within an error of a few percent, with the inverse ratio of clock frequencies. Indeed, careful study of published benchmarks tends to support this argument.

The empirical observation that computing performance is like architecture machines scales approximately with the clock frequency of the chip is useful, insofar as it allows us to relate achievable performance to Moore's Law, with some qualifying caveats. Mead observes that clock speeds scale with the ratio of geometry sizes, as compared to transistor counts which scale with the square of the ratio of geometry sizes. The interpretation of Moore's Law used in Figure 1.13 assumes this square root dependency, and incorporates a scaling factor to adjust the frequency to measured data. The plot in Figure 1.13 shows good agreement with Mead's model.

The conclusion that we can draw is that we will see a direct performance gain over time, proportional to the square root of the Moore's Law exponential, in machines with a given class of architecture. Since most equipment in operational use today is through prior history locked into specific architectures, such as Intel x86, SPARC, PowerPC, Alpha, MIPS and other, the near term consequence is that we will see performance increase exponentially with time for the life of the architecture.

However, major changes in internal architecture can produce further gains, at an unchanged clock speed. Therefore, the actual performance growth over time has been greater than that conferred by clock speed gains alone. Higher transistor counts allow for more elaborate internal architectures, thereby coupling performance gains to the exponential growth in transistor counts, in a manner which is not easily scaled like clock speeds. This effect was observed in microprocessors with the introduction of pipelining in the 1980s, superscalar processing in the 1990s and will be soon observed again with the introduction of VLIW architectures over the next two years. Since we are also about to observe the introduction of copper metallization during this period, replacing aluminum which has been used since the sixties, we can expect to see a slight excursion above the curve predicted by Moore's Law.

This behaviour relates closely to the second major question, which is that of the anticipated valid lifetime of Moore's Law. Many predictions have been made over the last two decades in relation to its imminent end. However, to date every single obstacle in semiconductor fab processes and packaging has been successfully overcome.

It is not difficult to observe that the limits on the scaling of transistor sizes and thus the achievable transistor counts per die are bounded by quantum physical effects. At some point, carriers will tunnel between structures, rendering transistors unusable and insulators leaky, beyond some point the charge used to define logical states will shrink down to the proverbial single electron.

The bounds for microprocessors are less clear, especially with emerging technologies such as Quantum Dot Transistors (QDT), with sizes of the order of 10 nm, as compared to current MOS technology devices which are at least twenty times larger 4. It follows that extant and nascent semiconductor component technologies should be capable of supporting further density growth until at least 2010. We cannot accurately predict further process improvements beyond that time, which accords well with "Mead's Rule" and its projection of 11 years.

However, there is considerable further potential for performance growth in machine architectures. To date most architectural evolution seen in microprocessors has been little more than the reimplementation of architectural ideas used in 1960s and 1970s mainframes, minicomputers and supercomputers, made possible by larger transistor counts. We have seen little architectural innovation in recent decades, and only modest advances in parallel processing techniques.

The achievable performance growth resulting from the adoption of VLIW architectures remains to be seen. While these offer much potential for performance growth through instruction level parallelism, they do not address the problems of parallel computation on multiple processors, and it is unclear at this time how well they will scale up with larger numbers of execution units in processors.

It would be naive to assume that we have already wholly exhausted the potential for architectural improvements in conventional Von-Neumann model stored program machines. Indeed if history teaches us anything, it is that well entrenched technologies can be wiped out very rapidly by new arrivals: the demise of the core memory under the onslaught of the MOS semiconductor memory is a classical case study, as is the GMR read head on the humble disk drive, which rendered older head technologies completely uncompetitive over a two-year period.

It may well be that quantum physical barriers will not be the limiting factor in microprocessor densities and clock speeds, rather the problems of implementing digital logic to run at essentially microwave carrier frequencies will become the primary obstacle to higher clock speeds.

The current trend to integrate increasingly larger portions of the computer system on a single die will continue, alleviating the problem in the medium term; however a 2020 microprocessor running at a 60 GHz clock speed is an unlikely proposition using current design techniques. Vector processing supercomputers built from discreet logic components reached insurmountable barriers of this ilk at hundreds of megahertz, and have become a legacy technology as a result.

Do other alternatives to the monolithic Silicon chip exist? Emerging technologies such as quantum computing and nano-technology both have the potential to further extend performance beyond the obstacles currently looming on the 2010-2020 horizons. Neural computing techniques, Mead argues, have the potential to deliver exponential performance growth with size, rather than speed, in the manner predicted for as yet unrealized highly parallel architectures.

It follows that reaching the speed and density limits of semiconductor technology may mean the end of exponential growth in single chip density and clock speeds, but it is no guarantee that the exponential growth in compute performance will slow down.

What we can predict with a high level of confidence is that Moore's Law will hold for the coming decade, and exponential growth is very likely to continue beyond that point.

Explain the Concept of Moore's Law.

# **1.4 Microprocessor Instruction Set**

Instructions can be categorized according to their method of addressing the hardware registers and/or memory.

#### 1.4.1 Implied Addressing

The addressing mode of certain instructions is implied by the instruction's function. For example, the STC (set carry flag) instruction deals only with the carry flag, the DAA (decimal adjust accumulator) instruction deals with the accumulator.

#### 1.4.2 Register Addressing

Quite a large set of instructions call for register addressing. With these instructions, you must specify one of the registers A through E, H or L as well as the operation code. With these instructions, the accumulator is implied as a second operand. For example, the instruction CMP E may be interpreted as 'compare the contents of the E register with the contents of the accumulator.

Most of the instructions that use register addressing deal with 8-bit values. However, a few of these instructions deal with 16-bit register pairs. For example, the PCHL instruction exchanges the contents of the program counter with the contents of the H and L registers.

#### 1.4.3 Immediate Addressing

Instructions that use immediate addressing have data assembled as a part of the instruction itself. For example, the instruction CPI 'C' may be interpreted as 'compare the contents of the accumulator with the letter C'. When assembled, this instruction has the hexadecimal value FE43. Hexadecimal 43 is the internal representation for the letter C. When this instruction is executed, the processor fetches the first instruction byte and determines that it must fetch one more byte. The processor fetches the next byte into one of its internal registers and then performs the compare operation.

Notice that the names of the immediate instructions indicate that they use immediate data. Thus, the name of an add instruction is ADD; the name of an add immediate instruction is ADI.

All but two of the immediate instructions use the accumulator as an implied operand, as in the CPI instruction shown previously. The MVI (move immediate) instruction can move its immediate data to any of the working registers including the accumulator or to memory. Thus, the instruction MVI D, OFFH moves the hexadecimal value FF to the D register.

The LXI instruction (load register pair immediate) is even more unusual in that its immediate data is a 16-bit value. This instruction is commonly used to load addresses into a register pair. As mentioned previously, your program must initialize the stack pointer; LXI is the instruction most commonly used for this purpose. For example, the instruction LXI SP,3OFFH loads the stack pointer with the hexadecimal value 30FF.

#### 1.4.4 Direct Addressing

Jump instructions include a 16-bit address as part of the instruction. For example, the instruction JMP 1000H causes a jump to the hexadecimal address 1000 by replacing the current contents of the program counter with the new value 1000H.

Instructions that include a direct address require three bytes of storage: one for the instruction code, and two for the 16-bit address.

#### 1.4.5 Register Indirect Addressing

Register indirect instructions reference memory via a register pair. Thus, the instruction MOV M, C moves the contents of the C register into the memory address stored in the H and L register pair. The instruction LDAX B loads the accumulator with the byte of data specified by the address in the B and C register pair.

#### 1.4.6 Combined Addressing Modes

Some instructions use a combination of addressing modes. A CALL instruction, for example, combines direct addressing and registers indirect addressing. The direct address in a CALL

instruction specifies the address of the desired subroutine; the register indirect address is the stack pointer. The CALL instruction pushes the current contents of the program counter into the memory location specified by the stack pointer.

1.4.7 Timing Effects of Addressing Modes

Addressing modes affect both the amount of time required for executing an instruction and the amount of memory required for its storage. For example, instructions that use implied or register addressing, execute very quickly since they deal directly with the processor's hardware or with data already present in hardware registers. Most important, however, is that the entire instruction can be fetched with a single memory access. The number of memory accesses required is the single greatest factor in determining execution timing. More memory accesses therefore require more execution time. A CALL instruction, for example, requires five memory accesses: three to access the entire instruction and two more to push the contents of the program counter onto the stack.

The processor can access memory once during each processor cycle. Each cycle comprises a variable number of states. The length of a state depends on the clock frequency specified for your system, and may range from 480 nanoseconds to 2 microseconds. Thus, the timing for a four-state instruction may range from 1.920 microseconds through 8 microseconds. (The 8085 have a maximum clock frequency of 5 MHz and therefore a minimum state length of 200 nanoseconds.)

Create the set of assembly language instruction for the simple microprocessor.

# 1.4.8 Decoding

The instruction decoder needs to turn each of the opcodes into a set of signals that drive the different components inside the microprocessor. Let's take the ADD instruction as an example and look at what it needs to do:

- 1. During the first clock cycle, we need to actually load the instruction. Therefore the instruction decoder needs to:

- activate the tri-state buffer for the program counter

- activate the RD line

- activate the data-in tri-state buffer

- latch the instruction into the instruction register

- 2. During the second clock cycle, the ADD instruction is decoded. It needs to do very little:

- set the operation of the ALU to addition

- latch the output of the ALU into the C register

- 3. During the third clock cycle, the program counter is incremented (in theory this could be overlapped into the second clock cycle).

Every instruction can be broken down as a set of sequenced operations like these that manipulate the components of the microprocessor in the proper order. Some instructions, like this ADD instruction, might take two or three clock cycles. Others might take five or six clock cycles.

The mnemonics assigned to the instructions are designed to indicate the function of the instruction.

Notes

# History and Evolution of Microprocessors

The invention of the transistor in 1947 was a significant development in the world of technology. It could perform the function of a large component used in a computer in the early years. Shockley, Brattain and Bardeen are credited with this invention and were awarded the Nobel Prize for the same. Soon it was found that the function of this large component was easily performed by a group of transistors arranged on a single platform. This platform, known as the integrated chip (IC), turned out to be a very crucial achievement and brought along a revolution in the use of computers. A person named Jack Kilby of Texas Instruments was honoured with the Nobel Prize for the invention of IC, which laid the foundation on which microprocessors were developed. At the same time, Robert Noyce of Fairchild made a parallel development in IC technology for which he was awarded the patent.

ICs proved beyond doubt that complex functions could be integrated on a single chip with a highly developed speed and storage capacity. Both Fairchild and Texas Instruments began the manufacture of commercial ICs in 1961. Later, complex developments in the IC led to the addition of more complex functions on a single chip. The stage was set for a single controlling circuit for all the computer functions. Finally, Intel corporation's Ted Hoff and Frederico Fagin were credited with the design of the first microprocessor.

The work on this project began with an order from a Japanese calculator company Busicom to Intel, for building some chips for it. Hoff felt that the design could integrate a number of functions on a single chip making it feasible for providing the required functionality. This led to the design of Intel 4004, the world's first microprocessor. The next in line was the 8-bit 8008 microprocessor. It was developed by Intel in 1972 to perform complex functions in harmony with the 4004.

This was the beginning of a new era in computer applications. The use of mainframes and huge computers was scaled down to a much smaller device that was affordable to many. Earlier, their use was limited to large organizations and universities. With the advent of microprocessors, the use of computers trickled down to the common man. The next processor in line was Intel's 8080 with an 8-bit data bus and a 16-bit address bus. This was amongst the most popular microprocessors of all time.

Very soon, the Motorola corporation developed its own 6800 in competition with the Intel's 8080. Fagin left Intel and formed his own firm Zilog. It launched a new microprocessor Z80 in 1980 that was far superior to the previous two versions. Similarly, a break off from Motorola prompted the design of 6502, a derivative of the 6800. Such attempts continued with some modifications in the base structure.

The use of microprocessors was limited to task-based operations specifically required for company projects such as the automobile sector. The concept of a 'personal computer' was still a distant dream for the world and microprocessors were yet to come into personal use. The 16-bit microprocessors started becoming a commercial sell-out in the 1980s with the first popular one being the TMS9900 of Texas Instruments.

Intel developed the 8086 which still serves as the base model for all latest advancements in the microprocessor family. It was largely a complete processor integrating all the required features in it. 68000 by Motorola was one of the first microprocessors to develop the concept of microcoding in its instruction set. They were further developed to 32 bit architectures. Similarly, many players like Zilog, IBM and Apple were successful in getting their own products in the market. However, Intel had a commanding position in the market right through the microprocessor era.

Contd...

The 1990s saw a large-scale application of microprocessors in the personal computer applications developed by the newly formed Apple, IBM and Microsoft corporation. It witnessed a revolution in the use of computers, which by then was a household entity.

Notes

This growth was complemented by a highly sophisticated development in the commercial use of microprocessors. In 1993, Intel brought out its 'Pentium Processor' which is one of the most popular processors in use till date. It was followed by a series of excellent processors of the Pentium family, leading into the 21st century. The latest one in commercial use is the Pentium Dual Core technology and the Xeon processor. They have opened up a whole new world of diverse applications. Supercomputers have become common, owing to this amazing development in microprocessors.

#### Questions:

- 1. Give the inventing year of transistor in the history of microprocessor.

- 2. Which company developed the first microprocessors?

# 1.5 Summary

- A microprocessor is designed to perform arithmetic and logic operations that make use of small number-holding areas called *registers*.

- Microprocessor is a silicon chip that contains a CPU.

- Bandwidth is the number of bits processed in a single instruction.

- The speed of the microprocessor is measured in MHz or GHz.

- Pentium 4 is the fastest type of the Intel's processor that contains 125,000,000 transistors and operates at the speed of 3.6 GHz.

- Microcomputers are designed to be used by individuals, whether in the form of PCs, workstations or notebook computers.

- Simple applications use only one ROM chip; the desktop calculator used four.

- One of the first users of the 8008 was Seiko in Japan for a sophisticated scientific calculator.

# 1.6 Keywords

Bandwidth: The number of bits processed in a single instruction.

BIOS: The basic input/output system that comes with the computer as part of its memory.

*EPROM*: Electrically programmed ROM's was significant in allowing customers to experiment with their software.

*Instruction set*: The set of instructions that the microprocessor can execute.

*The gate to pin ratio*: Optimization consists of maximizing the number of gates inside compared to the number of pins outside.

Lab Exercise

1. How do instructions run in the ROM? Explain.

2. Give some basic code of assembly language.

| 1.7 | Sel | f-Assessment Questions                                        |       |                                     |

|-----|-----|---------------------------------------------------------------|-------|-------------------------------------|

| 1.  | Мо  | st of the instructions that use register a                    | ddre  | essing deal with 8-bit values.      |

|     | (a) | 4-bit                                                         | (b)   | 16-bit                              |

|     | (c) | 8-bit                                                         | (d)   | None of these                       |

| 2.  | An  | can translate the words in                                    | to th | neir bit patterns very easily.      |

|     | (a) | assembler                                                     | (b)   | transistors                         |

|     | (c) | processor                                                     | (d)   | microprocessor                      |

| 3.  | The | e first microprocessor was (early 1970's)                     | ) use | d in calculators.                   |

|     | (a) | Intel 4040                                                    | (b)   | Intel 4400                          |

|     | (c) | Intel 8080                                                    | (d)   | Intel 4004                          |

| 4.  | An  | nicroprocessor is a computer processor                        | on a  | l                                   |

|     | (a) | minichip                                                      | (b)   | microchip                           |

|     | (c) | minicomputer                                                  | (d)   | None of these                       |

| 5.  |     | en your computer is turned on, the<br>ic input/output system. |       | gets the first instruction from the |

|     | (a) | microprocessor                                                | (b)   | microcomputer                       |

|     | (c) | microchip                                                     | (d)   | None of these                       |

| 6.  | Ou  | r program tells the CPU to perform wh                         | at is | called an                           |

|     | (a) | segment register                                              | (b)   | processor                           |

|     | (c) | interrupt                                                     | (d)   | None of these                       |

|     |     |                                                               |       |                                     |

## **1.8 Review Questions**

- 1. Define microprocessor in brief and also discuss its important areas.

- 2. Explain about microcomputers and its functions.

- 3. Explain in brief the fields in which microprocessors have brought changes.

- 4. Discuss in brief about Intel 8008 Microprocessor.

- 5. Explain microprocessor instruction set in brief.

- 6. What are the methods of addressing of Instructions?

- 7. Describe the instructions that affect the Stack and/or Stack Pointer.

- 8. What is assembly language? Discuss with the help of example.

- 9. Define decoding and its need.

- 10. What are the different types of chip? Discuss each of them.

#### **Answers for Self-Assessment Questions**

| 1. (c) 2. (a) 3. (d) 4. (b) 5. | (a) | 6. (c) |

|--------------------------------|-----|--------|

|--------------------------------|-----|--------|

# 1.9 Further Reading

Notes

Microprocessor 8085 Lab Manual, by: G.T. Swamy

http://www.webopedia.com/TERM/M/microprocessor.html. http://searchcio-midmarkessst.techtarget.com/definition/microprocessor.

# **Unit 2: Introduction to Assembly Language**

| CONTENTS                                  |  |  |  |  |

|-------------------------------------------|--|--|--|--|

| Objectives                                |  |  |  |  |

| Introduction                              |  |  |  |  |

| 2.1 Assembly Language                     |  |  |  |  |

| 2.1.1 Running the Program                 |  |  |  |  |

| 2.1.2 Opcodes and Operands                |  |  |  |  |

| 2.1.3 Labels                              |  |  |  |  |

| 2.1.4 Comments                            |  |  |  |  |

| 2.1.5 Pseudo-ops (Assembler Directives)   |  |  |  |  |

| 2.2 The Assembly Process                  |  |  |  |  |

| 2.3 Assembly Language Statements          |  |  |  |  |

| 2.4 Computer Languages                    |  |  |  |  |

| 2.4.1 Application Software Classification |  |  |  |  |

| 2.5 Summary                               |  |  |  |  |

| 2.6 Keywords                              |  |  |  |  |

| 2.7 Self-Assessment Questions             |  |  |  |  |

| 2.8 Review Questions                      |  |  |  |  |

| 2.9 Further Reading                       |  |  |  |  |

# Objectives

After studying this unit, you will able to understand the following:

- Explain Assembly Language

- Describe about Assembler Directives

- Discuss about Assessment Directives

- Explain the Assembly Process and Its Types

- Describe about the Assembly Language Statements

- Describe about Computer Languages

- Application Software Classification

# Introduction

This is a brief introduction to assembly language. Assembly language is the most basic programming language available for any processor. With assembly language, a programmer works only with operations implemented directly on the physical CPU. Assembly language lacks high-level conveniences such as variables and functions, and it is not portable between various families of processors. Nevertheless, assembly language is the most powerful computer programming language available, and it gives programmers the insight required to write effective code in high-level languages. Learning assembly language is well worth the time and effort of every serious programmer.

Before we can explore the process of writing computer programs, we have to go back to the basics and learn exactly what a computer is and how it works. Every computer, no matter how simple or complex, has at its heart exactly two things: a CPU and some memory. Together, these two things are what make it possible for your computer to run programs.

On the most basic level, a computer program is nothing more than a collection of numbers stored in memory. Different numbers tell the CPU to do different things. The CPU reads the numbers one at a time, decodes them, and does what the numbers say. For example, if the CPU reads the number 64 as part of a program, it will add 1 to the number stored in a special location called AX. If the CPU reads the number 146, it will swap the number stored in AX with the number stored in another location called BX. By combining many simple operations such as these into a program, a programmer can make the computer perform many incredible things.

As an example, here are the numbers of a simple computer program: 184, 0, 184, 142, 216, 198, 6, 158, 15, 36, 205, 32.

# 2.1 Assembly Language

Although the numbers of the above program make perfect sense to a computer, they are about as clear as mud to a human. Who would have guessed that they put a dollar sign on the screen? Clearly, entering numbers by hand is a lousy way to write a program.

It doesn't have to be this way, though. A long time ago, someone came up with the idea that computer programs could be written using words instead of numbers. A special program called an *assembler* would then take the programmer's words and convert them to numbers that the computer could understand. This new method, called writing a program in *assembly language*, saved programmers thousands of hours, since they no longer had to look up hard-to-remember numbers in the backs of programming books, but could use simple words instead.

The program above, written in assembly language, looks like this:

| MOV | AX,     | 47104 |

|-----|---------|-------|

| MOV | DS,     | AX    |

| MOV | [3998], | 36    |

| INT | 32      | 2     |

When an assembler reads this sample program, it converts each line of code into one CPU-level instruction. This program uses two types of instructions, MOV and INT. On Intel processors, the MOV instruction moves data around, while the INT instruction transfers processor control to the device drivers or operating system.

The program still isn't quite clear, but it is much easier to understand than it was before. The first instruction, MOV AX, 47104, tells the computer to copy the number 47104 into the location AX. The next instruction, MOV DS, AX, tells the computer to copy the number in AX into the location DS. The next instruction, MOV [3998], 36 tells the computer to put the number 36 into memory location 3998. Finally, INT 32 exits the program by returning to the operating system.

Before we go on, we would like to explain just how this program works. Inside the CPU are a number of locations, called registers, which can store a number. Some registers, such as AX, are general purpose, and don't do anything special. Other registers, such as DS, control the way the CPU works. DS just happens to be a *segment register*, and is used to pick which area of memory the CPU can write to. In our program, we put the number 47104 into DS, which tells the CPU to access the memory on the video card. The next thing our program does is to put the number 36 into location 3998 of the video card's memory. Since 36 is the code for the dollar sign, and 3998 is the memory location of the bottom right-hand corner of the screen, a dollar sign shows up on the screen a few microseconds later. Finally, our program tells the CPU to perform what is called an

#### Notes

interrupt. An interrupt is used to stop one program and execute another in its place. In our case, we want interrupt 32, which ends our program and goes back to MS-DOS, or whatever other program was used to start our program.

#### 2.1.1 Running the Program

Let's go ahead and run this program. First, be sure to print these instructions out, since you will need to refer to them as we go on. Next, click on your start menu, and run the program called MS-DOS Prompt. A black screen with white text should appear. We are now in MS-DOS, the way computers used to be 20 years ago. MS-DOS was before the days of the mouse, so you must type commands on the keyboard to make the computer do things.

First, we want you to type the word debug, and press enter. The cursor should move down a line, and you should see the Debug prompt, which is a simple dash. We are now in a program called *Debug*. Debug is a powerful utility that lets you directly access the registers and memory of your computer for various purposes. In our case, we want to enter our program into memory and run it, so we'll use Debug's a command, for assemble. Go ahead and type a100 now. The cursor will move down another line, and you will see something like 1073:0100. This is the memory location we are going to enter assembly language instructions at. The first number is the segment, and the second number is the memory location within the segment. Your Debug program will probably pick a different segment for your program than mine did, so don't worry if it's different. Another thing to note is that Debug only understands hexadecimal numbers, which are a sort of computer shorthand. Hexadecimal numbers sometimes contain letters as well as well as digits.

Let's go ahead and enter our program now. Type each of the instructions below into Debug exactly as they appear, and press enter after each one. When you finish entering the last instruction, press enter twice to tell Debug that we are done entering instructions.

```

mov ax,B800

mov ds,ax

mov byte[0F9E],24

int 20

```

As you can see, we have converted all the numbers into hexadecimal, and have made a few other changes so Debug can understand what's going on. If you make a mistake while entering the above program, press enter twice, type a100, and start entering instructions again at the beginning of the program.

Once you have entered the program, you can go ahead and run it. Simply type g for *go* and press enter when you are ready to start the program.

Let's get back to Windows now. Go ahead and type q to get out of Debug. Now, type exit to get out of MS-DOS. You should now be back in Windows.

#### 2.1.2 Opcodes and Operands

Two of the parts (OPCODE and OPERANDS) are **mandatory**. An instruction must have an OPCODE (the thing the instruction is to do), and the appropriate number of operands (the things it is supposed to do it to). The OPCODE is a symbolic name for the opcode of the corresponding LC-3b instruction. The idea is that it is easier to remember an operation by the symbolic name ADD, AND, or LDW than by the four-bit quantity 0001, 0101, or 0110. The number of operands depends on the operation being performed. For example, the ADD instruction (line 0E) requires three operands (two sources to obtain the numbers to be added, and one destination to designate where the result is to be placed). All three operands must be explicitly identified in the instruction.

#### AGAIN ADD R3, R3, R2

The operands to be added are obtained from register 2 and from register 3. The result is to be placed in register 3. We represent each of the registers 0 through 7 as R0, R2 - R7.

The LEA instruction (line 06) requires two operands (the memory location whose address is to be read) and the destination register which is to contain that address after the instruction completes execution. We will see momentarily that memory locations will be given symbolic addresses called labels. In this case, the location whose address is to be read is given the label NUMBER. The destination into which that address is to be loaded is register 2.

#### LEA R2, NUMBER

As we discussed in class, operands can be obtained from registers, from memory, or they may be literal (i.e. immediate) values in the instruction. In the case of register operands, the registers are explicitly represented (such as R2 and R3 in line 0C). In the case of memory operands, the symbolic name of the memory location is explicitly represented (such as NUMBER in line 06 and SIX in line 08). In the case of immediate operands, the actual value is explicitly represented (such as the value 0 in line 0A).

#### AND R3, R3; Clear R3

It will contain the product.

A literal value must contain a symbol identifying the representation base of the number. We use for decimal, x for hexadecimal, and b for binary. Sometimes there is no ambiguity, such as in the case 3F0A, which is a hex number. Nonetheless, we write it as x3F0A. Sometimes there is ambiguity, such as in the case 1000. X1000 represents the decimal number 4096, b1000 represents the decimal number 8, and 1000 represents the decimal number 1000.

1. Inside the CPU are a number of locations, called registers, which can store a number.

2. We use for decimal, x for hexadecimal, and b for binary.

#### 2.1.3 Labels

Labels are symbolic names which are used to identify memory locations that are referred to explicitly in the program. In LC-3b assembly language, a label consists of from one to 20 alphanumeric characters (i.e. a capital or lower case letter of the alphabet, or a decimal digit), starting with a letter of the alphabet. Now, Under21, R2D2, and C3PO are all examples of possible LC-3b assembly language labels.

There are two reasons for explicitly referring to a memory location:

- 1. The location contains the target of a branch instruction

- 2. The location contains a value that is loaded or stored.

The location AGAIN is specifically referenced by the branch instruction in line 10.

#### **BRP AGAIN**

If the result of ADD R, R1 is positive (as evidenced by the P condition code being set), then the program branches to the location explicitly referenced as AGAIN to perform iteration.

The location number is specifically referenced by the LEA instruction in line 06. The value stored in the memory location explicitly referenced as number is loaded into R2. If a location in the program is not explicitly referenced, then there is no need to give it a label.

END does not stop the program during execution. In fact, .END does not even exist at the time of execution. It is simply a delimiter; it marks the end of the source program.

#### 2.1.4 Comments

Comments are messages intended only for human consumption. They have no effect on the translation process and indeed are not acted on by the LC-3b Assembler. They are identified in the program by semicolons. A semicolon signifies that the rest of the line is a comment and is to be ignored by the assembler. If the semicolon is the first non-blank character on the line, the entire line is ignored. If the semicolon follows the operands of an instruction, then only the comment is ignored by the assembler.

The purpose of comments is to make the program more comprehensible to the human reader. They help explain a nonintuitive aspect of an instruction or a set of instructions. In line 0A, the comment "Clear R3; it will contain the product" lets the reader know that the instruction on line 0A is initializing R3 prior to accumulating the product of the two numbers. While the purpose of line 0A may be obvious to the programmer today, it may not be the case two years from now, after the programmer has written an additional 30,000 lines of code and cannot remember why he/she wrote AND R, R3, 0. It may also be the case that two years from now, the programmer no longer works for the company and the company needs to modify the program in response to a product update. If the task is assigned to someone who has never seen the code before, comments go a long way to helping comprehension.

It is important to make comments that provide additional insight and not just restate the obvious. There are two reasons for this. First, comments that restate the obvious are a waste of everyone's time. Second, they tend to obscure the comments that say something important because they add clutter to the program. For example, in line 0F, the comment "Decrement R1" would be a bad idea. It would provide no additional insight to the instruction, and it would add clutter to the page.

Another purpose of comments, and also the judicious use of extra blank spaces to a line, is to make the visual presentation of a program easier to understand. So, for example, comments are used to separate pieces of the program from each other to make the program more readable. That is, lines of code that work together to compute a single result are placed on successive lines, while pieces of a program that produce separate results are separated from each other. For example, note that lines 0E through 10 are separated from the rest of the code by lines 0D and 11. There is nothing on lines 0D and 11 other than the semicolons. Extra spaces that are ignored by the assembler provide an opportunity to align elements of a program for easier readability. For example, all the opcodes start in the same column on the page.

Prepare a program and use some of the instructions.

#### 2.1.5 Pseudo-ops (Assembler Directives)

The LC-3b assembler is a program that takes as input a string of characters representing a computer program written in LC-3b assembly language, and translates it into a program in the ISA of the LC-3b. Pseudo-ops are helpful to the assembler in performing that task. Actually, a more formal name for a pseudo-op is assembler directive. They are called pseudo-ops because they do not refer to operations that will be performed by the program during execution. Rather, the pseudo-op is strictly a message to the assembler to help the assembler in the assembly process. Once the assembler handles the message, the pseudo-op is discarded. The LC-3b assembler contains five pseudo-ops:

.ORIG, .FILL, .BLKW, .STRINGZ, and .END. All are easily recognizable by the dot as their first character.

Notes

#### .ORIG

.ORIG tells the assembler where in memory to place the LC-3b program. In line 05, .ORIG x3050 says, start with location x3050. As a result, the LEA R2, NUMBER instruction will be put in location x3050.

#### .FILL

.FILL tells the assembler to set aside the next location in the program and initialize it with the value of the operand. In line 15, the ninth location in the resultant LC-3b program is initialized to the value x0006.

### .BLKW

.BLKW tells the assembler to set aside some number of sequential memory locations (i.e. a Block of Words) in the program. The actual number is the operand of the .BLKW pseudo-op. In line 11, the pseudo-op instructs the assembler to set aside one location in memory (and also to label it NUMBER, incidentally).

The pseudo-op .BLKW is particularly useful when the actual value of the operand is not yet known. For example, one might want to set aside a location in memory for storing a character input from a keyboard. It will not be until the program is run that we will know the identity of that keystroke.

The argument is a sequence of n characters, inside double quotation marks. The first n 1 bytes of memory are initialized with the ASCII codes of the corresponding characters in the string, followed by x00. A final byte x00 is added if necessary to end the string on a word boundary. The n 1*st* character (x00) provides a convenient sentinel for processing the string of ASCII codes.

For example, the code fragment

```

.ORIG x3010

HELLO .STRINGZ "Hello, World!"

```

would result in the assembler initializing locations x3010 through x301D to the following values:

| x3010: | x48 |

|--------|-----|

| x3011: | x65 |

| x3012: | x6C |

| x3013: | x6C |

| x3014: | x6F |

| x3015: | x2C |

| x3016: | x20 |

| x3017: | x57 |

| x3018: | хбF |

| x3019: | x72 |

| x301A: | x6C |

| x301B: | x64 |

| x301C: | x21 |

| x301D: | x00 |

#### .END

.END tells the assembler where the program ends. Any characters that come after .END will not be utilized by the assembler.

*Notes* .END does not stop the program during execution. In fact, .END does not even exist at the time of execution. It is simply a delimiter it marks the end of the source program.

Sometimes there is no ambiguity, such as in the case 3F0A, which is a hex number, then, we write it as x3F0A.

# 2.2 The Assembly Process

Before an LC-3b assembly language program can be executed, it must first be translated into a machine language program, that is, one in which each instruction is in the LC-3b ISA. It is the job of the LC-3b assembler to perform that translation.

#### A Two-Pass Process

In this section, we will see how the assembler goes through the process of translating an assembly language program into a machine language program. You remember that there is in general a one-to-one correspondence between instructions in an assembly language program and instructions in the final machine language program. We could attempt to perform this translation in one pass through the assembly language program, the assembler discards lines 01 to 09, since they contain only comments. Comments are strictly for human consumption; they have no bearing on the translation process. The assembler then moves on to line 0A. Line 0A is a pseudo-op; it tells the assembler that the machine language program is to start a location x3000. The assembler then moves on to line 0B, which it can easily translate into LC-3b machine code. At this point, we have

#### X3000: 0101010010100000

The LC-3b assembler moves on to translate the next instruction (line 0C). Unfortunately, it is unable to do so, since it does not know the meaning of the symbolic address, PTR. At this point the assembler is stuck, and the assembly process fails.

To prevent the above problem from occurring, the assembly process is done in two complete passes (from beginning to .END) through the entire assembly language program. The objective of the first pass is to identify the actual binary addresses corresponding to the symbolic names (or labels). This set of correspondences is known as the *symbol table*. In pass one, we construct the symbol table. In pass two, we translate the individual assembly language instructions into their corresponding machine language instructions.

Thus, when the assembler examines line 0C for the purpose of translating LEA R3, PTR during the second pass, it already knows the correspondence between PTR and x3028 (from the first pass). Thus it can easily translate line 0C to x3002: 1110011000010011

The problem of not knowing the 16-bit address corresponding to PTR no longer exists.

#### The First Pass: Creating the Symbol Table

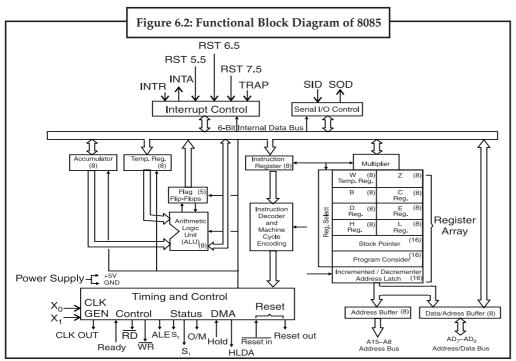

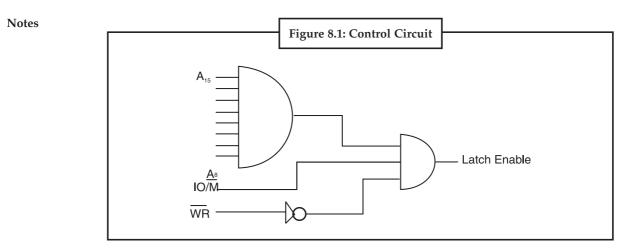

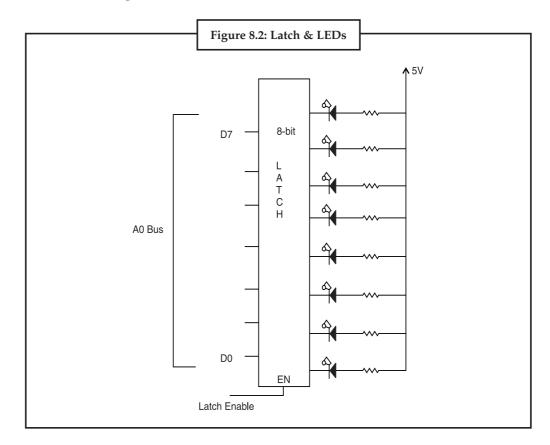

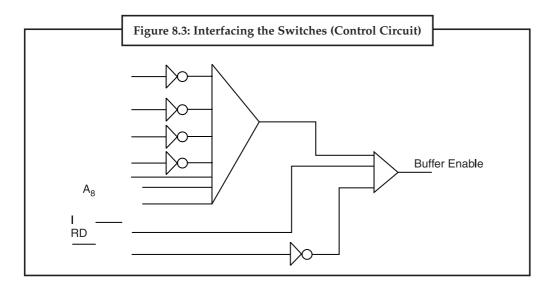

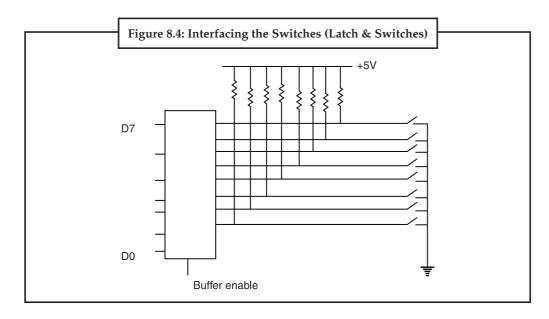

For our purposes, the symbol table is simply a correspondence of symbolic names with their 16bit memory addresses. We obtain these correspondences by passing through the assembly language program once, noting which instruction is assigned to which address, and identifying each label with the address of its assigned entry. Recall that we provide labels in those cases where we have to refer to a location, either because it is the target of a branch instruction or because it contains data that must be loaded or stored. Consequently, if we have not made any programming mistakes, and if we identify all the labels, we will have identified all the symbolic addresses used in the program.