# DEPARTMENT OF APPLIED CIENCES LASER DIVISION

# DIGITAL ELECTRONICS LECTURE NOTES

4<sup>TH</sup> YEAR

WALID K. HAMOUDEI

# Summary of basic electronic parameters and components

**Voltage:** Voltage is the difference in charge between two points, measured in Volts. **Current:** Current is the flow of electrons through a conductor or semiconductor, measured in Amperes or Amps. Some materials conduct current better than others; these are known as conductors, semiconductors, and insulators. Current flow is from positive to negative. **Power:** Power determines how much work a circuit can do. It is measured in Watts (Watts = Volts \* Amps).

**Ground:** Minimum voltage reference level. True ground connects to the earth but the circuits we work with may not actually be connected to the earth, especially if they are battery powered. Technically this is known as a floating ground.

### Resistance

Resistors are measured in Ohm and come between conductors, which conduct easily and insulators which don't conduct. The main function of resistors in a circuit is to control the flow of current and voltage drops to other components. For example; if too much current flows through an LED it is destroyed and will not light, so a resistor is used to limit the current but not so big as it will limit all the current. When a current flows through a resistor, energy is wasted and the resistor heats up. This will only be noticed if the resistor is working at its maximum power rating. The greater the current flowing through the resistor the hotter it gets. A battery or power supply has to do work to force electrons through the resistor and this work ends up as heat energy in the resistor. An important property to know about resistors is how much heat energy it can withstand before it's damaged or causes a fire. Resistors can dissipate different powers (Watts) depending on its power rating and the current passing through. It is difficult to make a resistor to an exact value, so resistances are given a tolerance. This is expressed as being plus or minus a percentage. A  $\pm 10\%$  resistor with a stated value of 100 ohms could have a resistance anywhere between 90 ohms and 110 ohms. In circuit diagrams you will often see an 'R' instead of omega to represent ohms. The symbol and a few examples of this type are shown below:

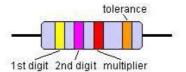

### **Resistor Color Code**

The resistor color code is a way of showing the value of a resistor. Instead of writing the resistance on its body, which would often be too small to read, a color code is used. Different colors represent the numbers 0 to 9. The first two colored bands on the body are the first two digits of the resistance, and the third band is the 'multiplier'. Multiplier just means the number of zeroes to add after the first two digits. Red represents the number 2, so a resistor with red, red, red bands has a resistance of 2 followed by 2 followed by 2 zeroes, which is 2200 ohms or 2.2 kilo Ohms. The final band is the tolerance (the accuracy  $\pm$  x %). All resistors have a tolerance which is shown by the last band.

| Color  | 1st Band | 2nd Band | 3rd Band | 4th Band |

|--------|----------|----------|----------|----------|

| Black  | 0        | 0        | 1        |          |

| Brown  | 1        | 1        | 10       |          |

| Red    | 2        | 2        | 100      |          |

| Orange | 3        | 3        | 1000     |          |

| Yellow | 4        | 4        | 10000    |          |

| Green  | 5        | 5        | 100000   |          |

| Blue   | 6        | 6        | 1000000  |          |

| Purple | 7        | 7        |          |          |

| Grey   | 8        | 8        |          |          |

| White  | 9        | 9        |          |          |

| Red    |          |          |          | 1%       |

| Gold   |          |          |          | 5%       |

| Silver |          |          |          | 10%      |

### **Examples:**

\*Yellow, Purple, Red, Gold = 47 x 100 = 4 700  $\Omega$  = 4.7 k $\Omega$  + 5% \*Brown, Black, Yellow, Gold = 10 x 10 000 = 100 k $\Omega$  + 5% \*Yellow, Purple, Black, Silver = 47 x 1 = 47  $\Omega$  + 10% \*Brown, Black, Red, Red = 10 x 100 = 1 000  $\Omega$  = 1 k $\Omega$  + 1% \*Brown, Black, Green, Gold = 10 x 100 000 = 1 000 k $\Omega$  = 1 M $\Omega$  + 5%

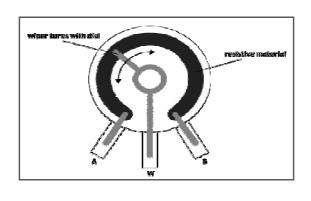

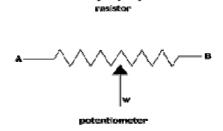

**Potentiometer:** It is a variable resistor, a wiper moves between two leads and the resistance between wiper and lead determines resistance. Resistance between leads is maximum resistance of potentiometer. With linear pots, resistance varies directly with the rotation of the knob while with logarithmic pots; resistance varies exponentially with the rotation of the knob.

Ohms Law: Every circuit has Voltage, Current and Resistance.

V=IR. Voltage = Current \* Resistance.

I=V/R. Current = Voltage/Resistance.

R=V/I. Resistance = Voltage/Current.

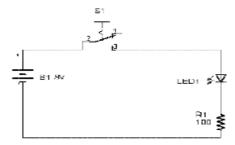

**Circuits:** A working circuit must have a closed loop of current flow through a load. The sum of the current entering a junction equals the sum of the current exiting a junction. Kirchoff's current law is:  $I_{in} = I_{out}$ . A circuit with a break in it is called an open circuit. A circuit without enough resistance in its load is called a short circuit. Switching an LED is shown at the example schematic below.

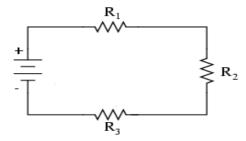

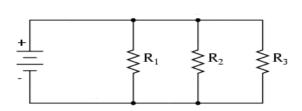

**Series Circuits:** All components are connected end to end. Single path for electrons to flow - all components share the same current. Total resistance of circuit is equal to sum of individual resistances. Total voltage in the circuit is equal to the sum of individual voltage drops.

**Parallel Circuits:** All components are connected in parallel and share the same voltage. The total resistance of circuit is less than the value after adding individual resistances. Total current in circuit is equal to sum of individual branch currents.

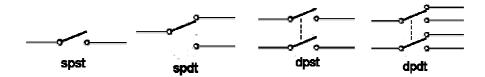

**Switches:** Mechanical devices that interrupt current flow. It is characterized by number of poles and number of throws.

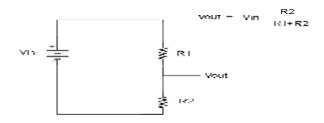

**Voltage divider:** With two resistors in series, the sum of the voltage drop across each equals the total voltage drop across both. To determine the voltage between the two resistors, we use the voltage divider formula;  $V_{out} = V_{in} * (R2/R1+R2)$

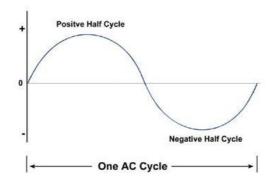

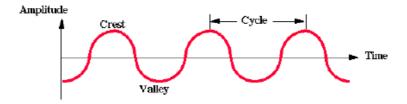

**Alternating Current:** AC Voltage alternates sinusoidal with time. AC Voltages are specified with a value equal to the DC voltage capable of doing the same amount of work. This value is  $1/\sqrt{2}$  times the peak voltage and is called the root means square or rms voltage.  $1/\sqrt{2} = 0.707$ . Household line voltages are specified at 240 Vac, meaning peak voltage is about 363v. An AC voltage can have a DC component and vice versa.

**Inductors:** Their values are measured in Henry and are commonly used as AC filters. By coiling wire we can increase strength of magnetic field created by current. This is called an inductor. A large inductor functions as an electromagnet. Strength of the magnetic field depends on number of coil turns, coil size, coil spacing, winding arrangement, core material, and shape of inductor.

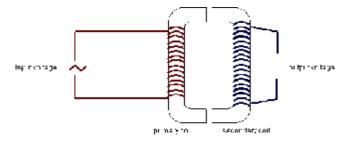

**Transformers:** Four terminal device which turns ac input voltage into a higher or lower output voltage. Transformers consist of two coils called primary and secondary sharing a common iron core. Ratio of turns between primary and secondary coil determines step up/step down value. Power (V\*I) is the same in the primary and secondary coil. Stepping down the voltage increases current while Stepping up the voltage decreases the current.

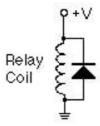

**Relays:** It is switch operated by an electromagnet and controlled by electrically isolated signal from switched current. It is slow, noisy and can pass AC or DC current. It generates unfriendly voltage spike when magnetic field in coil collapses.

**Inductive versus Resistive loads** Inductive loads use magnetic fields as in motors, solenoids, and relays. If it moves, it's probably an inductive load. They can cause blowback voltage and circuits should be protected from this by diodes. Blowback is caused by a surge of voltage created by the collapsing magnetic field in an inductor. Resistive loads convert current into other forms of energy, such as heat.

### **Capacitors**

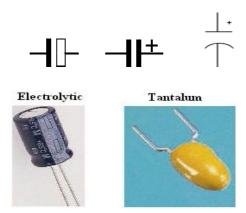

Capacitors are components that store an electrical charge. They can be charged up with energy from a battery, then return that energy back later. The capacitance of a capacitor is a measure of how much energy/charge it can store. In its simplest form a capacitor consists of two separated metal plates with air or another non-conductive material filling the gap, the bigger the plates the bigger the capacitance. To stop capacitors becoming impractically large they can be rolled up. Another way of increasing the capacitance is to put some non-conducting material between the plates. This is called a dielectric material. When a capacitor charges up, the protons and electrons in the dielectric separate out a little, this allows more charge to be stored on the plates than usual. Dielectrics are made of various materials Ceramic, paper, polyester, polystyrene, mica, etc. Capacitance is measured in Farads; one Farad is a very big unit and is usually found in the range of picot-to-micro farads. Capacitors come in two types, electrolytic and non-electrolytic. Electrolytic capacitors use special dielectrics sometimes a solid but the most common types are a liquid or paste which is formed into a very thin dielectric in the factory. Non-electrolytic capacitors have solid dielectrics. The symbol for electrolytic capacitors and a few examples of this type is shown below:

The symbol for non-electrolytic capacitors is shown below:

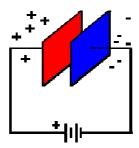

Electrolytic capacitors can store more charge but there are a couple of problems. They have a polarity and must be connected the right way around in a circuit. They also slowly leak their charge, and they have quite large tolerances i.e. 10% to 20%. Where as non-electrolytic capacitors still leak but not as fast as electrolytic and do not have a polarity problem but store less charge. When a capacitor is connected to a source it begins to charge. The current flows rapidly at first then more slowly as it gets to maximum its charge. Charge builds up on the two plates, negative charge on one plate and the same amount of positive charge on the other. The positive charge results from electrons leaving one of the plates and leaving positively-charged protons behind. As the capacitor fills with charge, it starts to oppose the current flowing in the circuit. It is as if another battery were working against the first. The current decreases and the capacitor charges more slowly. The plates become full of charge when no current flows, and the circuit acts like an open type.

charging a capacitor through a resistor

If a capacitor is shorted then it discharges. Charge flows out of the capacitor rapidly at first, then progressively more slowly. The speed at which the capacitor empties or charges depends on the resistance. If a simple wire shorts out a capacitor then it empties in a flash, often with a spark if it's a big capacitor. We've mentioned that when a capacitor is fully charged the current stops. In other words a continuous current cannot flow through a capacitor. A continuous current is called a direct current or D.C. An alternating current (A.C.) however can flow through a capacitor. An alternating current is one which is continually changing its direction. The Mains is A.C. and changes its direction 50 times a second. An alternating current continually charges and discharges a capacitor and hence is able to keep current flowing.

Capacitors hold charge when disconnected from power supply. Dielectric keeps charge from jumping from one plate to another. Lightening is a giant capacitive charge discharging. 1 Farad is equal to 1 amp of current at 1 volt for 1 second. Capacitors we work with are typically measured in Micro- Farads ( $\mu F$ ) and Pico Farads (pF). Common uses of capacitors are camera flashes, lasers, decoupling noise, smoothing power supplies, timing etc.

Capacitors - RC Time: Capacitors take time to charge and discharge, according to the amount of current. The charge/discharge time of capacitors is controlled using resistors. Charge time (to 63.2% of supply voltage) and discharge time (to 36.8% of supply voltage) is nicely equal to R\*C (in seconds). RC Time allows us to control the rate that things happen in circuits, which turns out to be very useful.

Capacitor Types: Three major types of capacitors are ceramic, electrolytic, and tantalum. Ceramic capacitors are small in size and value, ranging from a few Pico Farads to 1  $\mu$ F. Not polarized, so either end can go to ground. Value is given by a code somewhat like that of resistors.

Electrolytic capacitors look like small cylinders and range in value from 1  $\mu F$  to several Farads. Very inaccurate and change in value as the electrolytic ages. Polarized, cathode must go to ground. Cathode is marked with a minus sign on case. Value is usually written on case.

Tantalum capacitors are similar in size to ceramic but can hold more charge, up to several hundred  $\mu F$ . Accurate and stable, but relatively expensive. Usually polarized anode is marked with a plus sign.

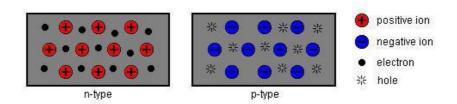

**Semiconductors:** It is probably the most important discovery in electronics which happened last century. Without this discovery we wouldn't have televisions, computers, space rocket, CD players, etc. Unfortunately it's also one of the hardest areas to understand in electronics. The reason that makes metals such good conductors is that they have lots of electrons which are so loosely held that they're easily able to move when a voltage is applied. Insulators have fixed electrons and so are not able to conduct. Certain materials, called semiconductors, are insulators that have a few loose electrons. They are partly able to conduct a current. The free electrons in semiconductors leave behind a fixed positive charge when they move about (the protons in the atoms they come from). Charged atoms are called ions. The positive ions in semiconductors are able to capture electrons from nearby atoms. When an electron is captured another atom in the semiconductor becomes a positive ion. This behavior can be thought of as a 'hole' moving about the material, moving in just the same way that electrons move. So now there are two ways of conducting a current through a semiconductor, electrons moving in one direction and holes in the other. The holes don't really move of course. It is just fixed positive ions grabbing neighboring electrons, but it appears as if holes are moving.

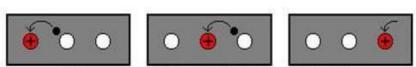

electrons moving to the left = 'holes' moving to the right

In a pure semiconductor there are not enough free electrons and holes to be of much use. Their number can be greatly increased however by adding an impurity, called a donor. If the donor gives up some extra free electrons we get an n-type semiconductor (n for negative). If the donor soaks up some of the free electrons we get a p-type semiconductor (p for positive). In both cases the impurity donates extra current carriers to the semiconductor. Adding impurities is called doping. In n-type semiconductors there are more electrons than holes and they are the main current carriers. In p-type semiconductors there are more holes than electrons and they are the main current carriers. The donor atoms become either positive ions (n-type) or negative ions (p-type).

The most common semiconductors are silicon (basically sand) and germanium. Common donors are arsenic and phosphorus. When we combine n-type and p-type semiconductors together we make useful devices, like transistors, diodes and chips.

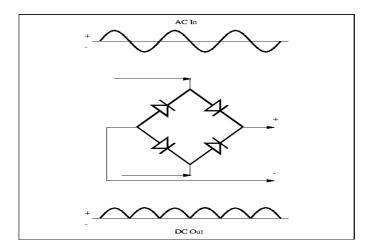

**The Diode:** Simplest useful semiconductor that allows current flow from anode to cathode but not in reverse. Cathode goes to ground.

## **Diode applications examples**

- 1) Reverse polarity protection.

- 2) Reverse biased diode in parallel with an inductive load will snub the blowback current generated by the collapsing magnetic field.

3) Rectifier converts AC into DC.

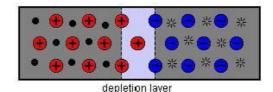

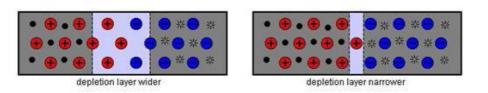

A diode consists of a piece of n-type and a piece of p-type semiconductor joined together to form a junction. Electrons in the n-type half of the diode are repelled away from the junction by the negative ions in the p-type region, and holes in the p-type half are repelled by the positive ions in the n-type region. A space on either side of the junction is left without either kind of current carriers. This is known as the depletion layer because there are no current carriers in this layer, so current can flow. The depletion layer is, in effect, an insulator.

Consider what would happen if we connected a small voltage to the diode. Connected one way it would attract the current carriers away from the junction and make the depletion layer wider. Connected the other way it would repel the carriers and drive them towards the junction, so reducing the depletion layer. In neither case would any current flow because there would always be some of the depletion layer left.

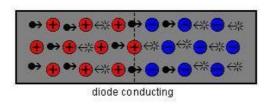

Now consider increasing the voltage. In one direction there is still no current because the depletion layer is even wider (reverse biased), but in the other direction the layer disappears completely and current can flow (forward biased). Above a certain voltage the diode acts like a conductor. As electrons and holes meet each other at the junction they combine and disappear.

Thus a diode is a device which is an insulator in one direction and a conductor in the other. Diodes are extremely useful components. We can stop currents going where we don't want them to go. For example we can protect a circuit against the battery being connected backwards which might otherwise damage it.

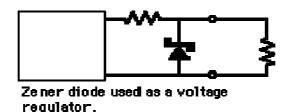

**Zener Diodes:** Conducts in reverse-bias direction at a specific breakdown voltage. It is used to provide reference voltage.

### **LED** (Light Emitting Diode)

Light emitting diodes (LEDS) are special diodes that give out light when they conduct. The fact that they only conduct in one direction is often incidental to their use in a circuit. They are usually just being used as lights. They are small and cheap and they last practically forever, unlike traditional light bulbs which can burn out. The light comes from the energy given up when electrons combine with holes at the junction. The color of the light depends on the impurity in the semiconductor. It is easy to make bright red, green and yellow LEDS but technology can't make cheap LEDS of other colors like white or blue. The symbol and a few examples of this type is shown below (Note the cathode on the component is shown as a flat edge or the

### The Transistor

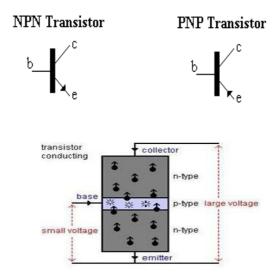

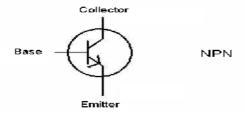

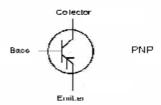

Transistors underpin the whole of modern day electronics. They are found in watches, calculators, microwaves, hi-fi's. A Pentium computer chip contains over a million transistors. Transistors work in two ways. They can work as switches (turning currents on and off) and as amplifiers (making currents bigger). When acting as an amplifier they operate in the linear mode and as a switch they are forced into saturation (on) or cut off (off). Transistors are sandwiches of three pieces of semiconductor material. A thin slice of n-type or p-type semiconductor is sandwiched between two layers of the opposite type. This gives two junctions rather than the one found in a diode. If the thin slice is n-type the transistor is called a p-n-p transistor,

and if the thin slice is p-type it is called an n-p-n transistor. The middle layer is always called the base, and the outer two layers are called the collector and the emitter. In an n-p-n transistor (more common), electrons are the main current carriers (because n-type material predominates). When no voltage is connected to the base then the transistor is equivalent to two diodes connected back to back. Recall that current can only flow one way through a diode. A pair of back-to-back diodes can't conduct at all. If a small voltage is applied to the base (enough to remove the depletion layer in the lower junction), current flows from emitter to base like a normal diode. Once current is flowing however it is able to sweep straight through the very thin base region and into the collector, only a small part of the current flows out of the base. The transistor is now conducting through both junctions. A few of the electrons are consumed by the holes in the p-type region of the base, but most of them go straight through.

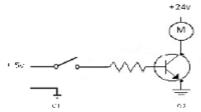

Electrons enter the emitter from the battery and come out of the collector. To see how a transistor acts as a switch, a small voltage applied to the base will switch the transistor on, allowing a current to flow in the rest of the transistor. NPN and PNP Transistor components look identical to each other the only way to tell the difference is by the component number. The symbol and a few examples of this type are shown below:

**Transistor Basics:** Use three layers of silicon and can be used as a switch or an amplifier. Processor chips are lots and lots of transistors in one package. Transistors have three leads - the base, collector and emitter.

**Bipolar versus Field Effect Transistors**: There are two main families of transistors, Bipolar and FET. FETs are more popular, waste less power (therefore run cooler), and are cheaper than bipolar. FETs can be easily damaged by static electricity, so this explains why bipolar types are used for teaching and training students. The basic operation of bipolar and FETs are the same.

**NPN versus PNP:** In NPN, the base is at a higher voltage than the emitter, current flows from collector to emitter. A small amount of current also flows from base to emitter. NPN Voltage at base controls amount of current flow through transistor (collector to emitter).

In PNP, the base is at a lower voltage than the emitter, current flows from emitter to collector. A small amount of current also flows from emitter to base. PNP. Voltage at base controls amount of current flow through transistor (emitter to collector). The arrow represents the direction of current flow.

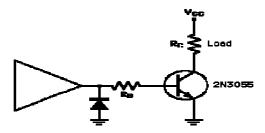

**Transistor as switch:** Most sensors, processors, microcontrollers can't source enough power to make things happen in the real world. Transistors allow a large amount of current to be controlled by a small change in voltage. Grounds between control circuit and transistor must be common.

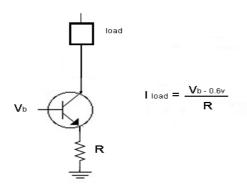

**Transistor as current source:** 1) Transistors have a fixed degree of amplification. ( $h_{FE}$ ). When a transistor is at maximum amplification it is saturated. Saturation works when we want to pass the maximum amount of current though the transistor. By limiting the voltage at the base, we can limit the current through the circuit. Somewhat against intuition, when we limit current with a transistor, it's called amplification, because the small amount of voltage at the base is controlling the large current flow;  $I_c = (V_{b^-} \ 0.6 \text{v})/R$

# Analog and Digital Signals

There are two different methods of sending an electronic signal from A to B. ANALOG signals are continuous, and can take any value. DIGITAL signals encode values into binary numbers. As a binary number is made up entirely from 0's and 1's, it may be transmitted in the form of electronic on/off pulses (on =1, off =0). When these pulses are received, they are processed. A digital signal is made up of discretely variable physical quantities.

Whilst these two types of signal both transmit information in electrical voltages, they each have their advantages and disadvantages. In recording audio signals, analog systems are useful, because they can give a faithful electronic representation of a complex waveform. However, because of the need for amplification of the electronic signal, 'noise' can be added along the signal path. This noise is due to unavoidable electron activity in the circuitry. Unfortunately, there is no easy way to get rid of noise from the original signal. Consequently, the noise (audible as a 'hiss') is added to the signal with each stage of transmission.

A digital equivalent to this system would sample the sound wave at selected intervals and transmit the values that correspond to the sound wave in binary code. The digital representation of the sound wave could then be moved around or processed within the system without picking up any additional noise. Although the electron (noise) activity is still taking place, whenever the digital signal is repeated, during each stage of the transmission, the noise can be omitted.

| Analog Signal                         | Digital Signal                         |

|---------------------------------------|----------------------------------------|

| Accurate reproduction of signal needs | Very immune from noise                 |

| extra work                            |                                        |

| Suffers from noise and distortion     | Output is accurate but can have errors |

|                                       | from the sampling process              |

| Simple technique                      | Complicated but can operate at long    |

|                                       | distance                               |

<u>Table 1</u> outlines the basic characteristics of 3 modulation (encoding transmission signal) schemes: <u>Amplitude modulation</u> (AM), <u>frequency modulation</u> (FM) (both analog schemes) and <u>digital modulation</u>.

| Table 1 - Comparison of AM, FM, and Digital Encoding Techniques |                                      |                            |                            |  |  |

|-----------------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|--|--|

| Parameter                                                       | AM                                   | FM                         | Digital                    |  |  |

| Signal-to-Noise <u>Ratio</u>                                    | Low-to-Moderate                      | Moderate-High              | High                       |  |  |

| Performance vs. <u>Attenuation</u>                              | Sensitive                            | Tolerant                   | Invariant                  |  |  |

| Transmitter Cost                                                | Moderate-High                        | Moderate                   | High                       |  |  |

| Receiver Cost                                                   | Moderate                             | Moderate-High              | High                       |  |  |

| Receiver Gain<br>Adjustment                                     | Often Required                       | Not Required               | Not Required               |  |  |

| Installation                                                    | Adjustments<br>Required              | No Adjustments<br>Required | No Adjustments<br>Required |  |  |

| Multi-channel<br>Capabilities                                   | Require High <u>Linearity</u> Optics | Fewer Channels             | Good                       |  |  |

| Performance Over Time                                           | Moderate                             | Excellent                  | Excellent                  |  |  |

| Environmental<br>Factors                                        | Moderate                             | Excellent                  | Excellent                  |  |  |

One difference between analog and digital transmission involves the bandwidth, or transmission capacity required for both schemes. Analog signals require much less bandwidth, only about 4.5 MHz with a 143.2 Mb/s data rate for the average video signal. By comparison, some digital video transmission standards require as much as 74.25 MHz with a data rate of 1485 Mb/s.

Another difference between analog and digital transmission deals with the hardware's ability to recover the transmitted signal. Analog modulation, which is continuously variable by nature, requires adjustment at the receiver end in order to reconstruct the transmitted signal. Digital transmission, however, because it uses only 1's and 0's to encode the signal, offers a simpler means of reconstructing the signal.

Both types of modulation can incorporate error detecting and error correcting information to the transmitted signal. However, the latest trend in signal transmission is <u>forward error correcting (FEC)</u>. This scheme, which uses <u>binary</u> numbers, is suited to digital transmission. Extra <u>bits</u> of information are incorporated into the digital signal, allowing any transmission errors to be corrected at the receiver end.

### **Analog Signal Transmission**

Analog transmission inserts signals of varying frequency or amplitude on carrier waves with a given frequency to produce a continuous wave. In a telephone system, an electric current or the reproduction of patterned sound waves are transmitted through a wire and into the telephone receiver. Once this is completed, they are then converted back into sound waves.

In digital transmission, the signals are converted into a binary code, which consists of two elements—positive (1) and non-positive (0). Every digit in a binary number is referred to as a bit and represents a power of two. As an example of digital transmission, in a type of digital telephone system, coded light signals travel through optical fibers and are then decoded by the receiver. When transmitting a telephone conversation, the light flashes on and off about 450 million times per second. This high rate enables two optical fibers to carry about 15,000 conversations simultaneously. Digital format is ideal for electronic communication as the string of 1s and 0s can be transmitted by a series of "on/off" signals represented by pulses of electricity or light. A pulse "on" can represent a 1, and the lack of a pulse "off" can represent a 0. Information in this form is very much easier to store electronically. Furthermore, digital transmission is usually faster and involves less noise and disturbances as compared to analog data transmission.

Analog signal transmission uses direct current (dc) variations in current or voltage to represent a data value used to communicate information. Most data acquisition signals can be described as analog, digital or pulse. While analog signals typically vary smoothly and continuously over time, digital signals are present at discrete points in time. Analog signals represent continuously variable entities such as temperatures, pressures, or flow rates. Because computer-based controllers and

systems understand only discrete on/off information, conversion of analog signals to digital representations is necessary. In analog signal transmission the wiring system can effectively reduce noise interference. Analog signal transmission employs two-wire signal leads or three-wire signal leads for high precision and accuracy. The third signal lead, or shield, is grounded at the signal source to reduce noise. There are many different wiring options that are available to reduce unwanted noise pickup from entering the line. Four types of wires are fundamental in data acquisition-plain pair, shielded pair, twisted pair, and coaxial cable.

- 1. Plain wire is not very reliable in screening out noise and is not suggested. A shielded pair is a pair of wires surrounded by a conductor that does not carry current. The shield blocks the interfering current and directs it to the ground. When using shielded pair, it is very important to follow the rules in grounding. Again, the shield must only be grounded at one source, eliminating the possibility of ground-loop currents.

- **2.** Twisted-pairs help in elimination of noise due to electromagnetic fields by twisting the two signal leads at regular intervals. Any induced disturbance in the wire will have the same magnitude and result in error cancellation.

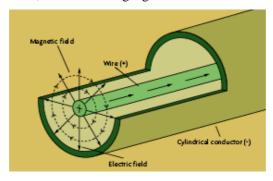

- **3.** A coaxial cable is another alternative for protecting data from noise. A coaxial cable consists of a central conducting wire separated from an outer conducting cylinder by an insulator. The central conductor is positive with respect to the outer conductor and carries a current. Coaxial cables do not produce external electric and magnetic fields and are not affected by them. This makes them ideally suited, although more expensive, for transmitting signals.

**Coaxial Cable Construction**

A sensor measures a variable by converting information about that variable into a dependent signal of either electrical or pneumatic nature. Cadmium sulfide resistance varies inversely and nonlinearly with light intensity and we can employ this device for light measurement. Analog signal conditioning provides the operations necessary to transform a sensor output into a form necessary to interface with other elements of the process-control loop.

We often describe the effect of the signal conditioning by the term transfer function. By this term we mean the effect of the signal conditioning on the input signal. Thus, a simple voltage amplifier has a transfer function of some constant that, when multiplied by the input voltage, gives the output voltage. **Signal conditioning** can be categorized into the following types:

### 1. Signal-Level Changes

The simplest method of signal conditioning is to change the level of a signal. The most common example is the necessity to either **amplify or attenuate a voltage level.** Generally, process-control applications result in slowly varying signals where dc or low-frequency response amplifiers can be employed. An important factor in the selection of an **amplifier is the input impedance that the amplifier offers to the sensor** (or any other element that serves as an input). In process control, the signals are always representative of a process variable. In accelerometers and optical detectors, the frequency response of the amplifier is very important.

### 2. Linearization

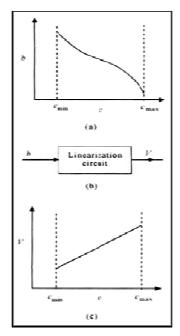

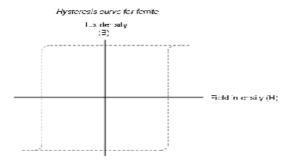

The process-control designer has little choice of the characteristics of a sensor output versus process variable. Often, the dependence that exists between input and output is nonlinear. Even those devices that are approximately linear may present problems when precise measurements of the variable are required. **Specialized analog circuits were devised to linearize signals.** For example, suppose a sensor output varied nonlinearly with a process variable, as shown in Figure-1a. A linearization circuit, indicated symbolically in Figure-1b, would condition the sensor output to produce voltage signal linear with the process variable, as shown in Figure -1c. The **modern approach to this problem is to provide the nonlinear signal as input to a computer and perform the linearization using software**.

FIGURE- 1: The purpose of linearization is to provide an output that varies linearly with some variable even if the sensor output does not.

### 3. Conversions

Often, signal conditioning is used to convert one type of electrical variation into another. Thus, a large class of sensors exhibit changes of resistance with changes in a dynamic variable. In these cases, it is necessary to convert this resistance change either to a voltage or a current signal. This is generally accomplished by bridges when the fractional resistance change is small and/or by amplifiers whose gain varies with resistance.

An important type of conversion is associated with the process-control standard of transmitting signals as 4-20 mA current levels in wire. This gives rise to the need for converting resistance and voltage levels to an appropriate current level at the transmitting end and for converting the current back to voltage at the receiving end. Thus, voltage-to-current and current-to-voltage converters are often required.

The use of computers in process control requires conversion of analog data into a digital format using analog-to-digital converters (ADCs). Analog signal conversion is usually required to adjust the analog measurement signal to match the input requirements of the ADC.

### 4. Filtering and Impedance Matching

In the industrial environment, signals of considerable strength are present, especially those generated at 60-Hz line frequency. Motor start transients also may cause pulses and other unwanted signals in the process-control loop. In many cases, it is necessary to use high-pass, low-pass, or notch filters to eliminate unwanted signals from the loop. Such filtering can be accomplished by *passive* filters using only resistors, capacitors, and inductors; or active filters, using gain and feedback. Impedance matching is an important element of signal conditioning when transducer internal impedance or line impedance can cause errors in measurement of a dynamic variable. Both active and passive networks are employed to provide such matching.

### 5. Concept of Loading

Loading of one circuit by another introduces uncertainty in the amplitude of a voltage as it is passed through the measurement process. If this voltage represents some process variable, then we have uncertainty in the value of the variable.

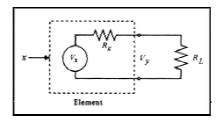

**Qualitatively**, loading can be described as follows. Suppose the open circuit output of some element is a voltage, say  $V_x$ , when the element input is some variable of value x. *Open circuit* means that nothing is connected to the output. Loading occurs when we connect a load across the output and the output voltage of the element drops to some value,  $V_y < V_x$ . Different loads will result in different drops.

Quantitatively, loading is evaluated as follows. Thevenin's theorem tells us that the output terminals of any element can be defined as a voltage source in series with output impedance (output resistance). This is often called the Thevenin's equivalent circuit model of the element.

FIGURE -2 The Thevenin's equivalent circuit of a sensor allows easy visualization of how loading occurs

Figure -2 shows such an element modeled as a voltage  $V_x$  and a resistance  $R_x$ . Now suppose a load,  $R_L$ , is connected across the output of the element as shown in Figure -2. This could be the input resistance of an amplifier. A **current will flow and voltage** will be **dropped across**  $R_x$ . The loaded output voltage will thus be given by:

$$V_{y} = V_{x} \left( 1 - \frac{R_{x}}{R_{L} + R_{c}} \right) \tag{2.1}$$

The voltage that appears across the load is reduced by the voltage dropped across the internal resistance. This equation shows how the effects of loading can be reduced after making  $R_L > R_X$ .

EXAMPLE 2.1

An amplifier outputs a voltage that is ten times the voltage on its input terminals. It has an input resistance of 10 kW. A sensor outputs a voltage proportional to temperature with a transfer function of 20 mV/°C. The sensor has an output resistance of  $5 \text{k}\Omega$ . If the temperature is 50 °C, find the amplifier output.

### **Solution**

the unloaded output of the sensor is simply  $V_T = (20 \text{ mV/°C}).50 \text{°C} = 1.0 \text{ V}$ . Since the amplifier has a gain of 10, the output of the amplifier appears to be  $V_{\text{out}} = 10 V_{\text{in}} = (10)1.0 \text{ V} = 10 \text{ V}$ . But this is wrong, because of loading since a voltage dropped will appear across the output resistance of the sensor. The actual amplifier input voltage will be given by Equation (2.1),

$$V_{cc} = V_{\tau} \left( 1 - \frac{5 \, k\Omega}{5 \, k\Omega + 10 \, k\Omega} \right)$$

Where  $V_T = 1.0$  volts, so that  $V_{in} = 0.67$  volts. Thus, the output of the amplifier is actually  $V_{out} = 10(0.67 \text{ V}) = 6.7 \text{ V}$ .

### **Analog and Digital Sound Representation:**

### **Signals**

When sound is transmitted, it may need to change form, without being destroyed.

Sound moves fast: in air, at 340 m/sec. Its two important characteristics are **Frequency** and **Amplitude**. Frequency is measured in Hz. Humans can hear frequencies between 20 Hz and 20,000 Hz. Amplitude is measured in decibels. Consider music:

- 1. Sound is pressure waves in air, caused by drums, guitar strings... etc or vocal cords

- 2. Converted to electrical signals by a microphone

- 3. Converted to magnetism when it's put on master tape and edited

- 4. Converted to spots on a CD when CD is manufactured

- 5. Converted to electricity when played by CD player

- 6. Converted back to sound by a speaker

A similar kind of story can be told about visual images (sequences of static images) stored on videotape or DVD and played on DVD player.

### **Degradation**

Any time signals are transmitted; there will be some degrading of quality:

- 1. signals may fade with time and distance

- 2. signals may get combined with interference from other sources (static)

- 3. signals may be chopped up or lost

When we continue to transmit and transform signals, the effect is compounded. Think about photocopies of photocopies of photocopies...

### **Example**

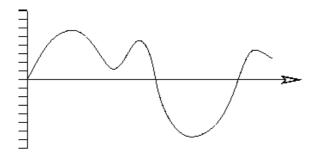

This is the transmitted signal:

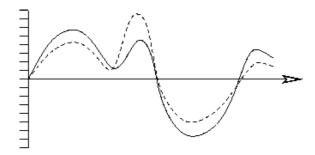

And this is the received signal (dashed) compared to the transmitted signal:

The horizontal axis here is time. The vertical axis is some physical property of the signal, such as electrical voltage, pressure of a sound wave, or intensity of light.

The degradation may not be immediately obvious, but there is a general lessening of strength and there is some noise added near the second peak.

### **Analog Signals**

The pictures above are examples of analog signals:

An analog signal varies some physical property, such as voltage, in proportion to the information that we are trying to transmit.

Examples of analog technology:

28

- 1. photocopiers

- 2. telephones

- 3. audio tapes

- 4. televisions (intensity and color info per scan line)

Analog signals always suffer from degradation.

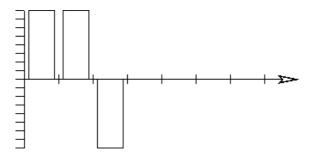

### **Digital Signals**

With a digital signal, we are using an analog signal to transmit numbers, which we convert into bits and then transmit the bits.

A digital signal uses some physical property, such as voltage, to transmit a single bit of information.

Suppose we want to transmit the number 6. In binary, that number is 110. We first decide that, say, "high" means 1 and "low" means 0. Thus, 6 might look like:

The line is the signal, which rises to the maximum to indicate a 1 and falls to the minimum to indicate a 0.

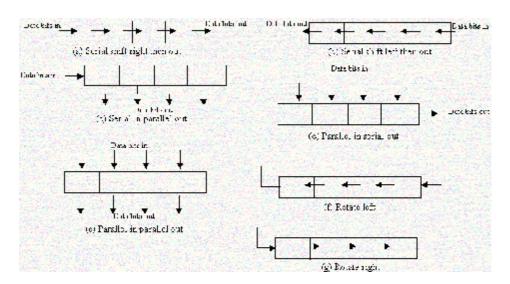

### Serial & Parallel

Serial and parallel transmission mechanisms are two ways of sending a digital signal from A to B.

A serial connection will send one line of data from transmitter to receiver. This method is electronically simpler, making it easier to determine what is going on, plus it's cheaper. It is, however, slower than parallel transmission.

29

Parallel transmission uses multiple lines of data to send more information more quickly. This method is more complex and more expensive than serial transmission. Also, it is usually only good for short distance transmissions of data.

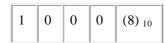

Computers process data in binary form, or base 2. The following table gives the binary equivalent values for 0-15 (decimal):

| Decimal |       | Bina  | ary            |                | Decimal |       | Bina  | ary            |                |

|---------|-------|-------|----------------|----------------|---------|-------|-------|----------------|----------------|

|         | $2^3$ | $2^2$ | 2 <sup>1</sup> | 2 <sup>0</sup> |         | $2^3$ | $2^2$ | 2 <sup>1</sup> | 2 <sup>0</sup> |

| 0       | 0     | 0     | 0              | 0              | 8       | 1     | 0     | 0              | 0              |

| 1       | 0     | 0     | 0              | 1              | 9       | 1     | 0     | 0              | 1              |

| 2       | 0     | 0     | 1              | 0              | 10      | 1     | 0     | 1              | 0              |

| 3       | 0     | 0     | 1              | 1              | 11      | 1     | 0     | 1              | 1              |

| 4       | 0     | 1     | 0              | 0              | 12      | 1     | 1     | 0              | 0              |

| 5       | 0     | 1     | 0              | 1              | 13      | 1     | 1     | 0              | 1              |

| 6       | 0     | 1     | 1              | 0              | 14      | 1     | 1     | 1              | 0              |

| 7       | 0     | 1     | 1              | 1              | 15      | 1     | 1     | 1              | 0              |

In a 4 line parallel connection, the decimal number 13 is communicated by sending one/on pulse along line 1  $(2^3)$ , one/on pulse along line 2  $(2^2)$ , zero/off pulse along line 3  $(2^1)$ and one/on pulse along line 4  $(2^0)$ . Computer memory is defined in terms of Bits and Bytes.

1 Bit = one on/off space in memory (0 or 1).

1 Byte = 8 bits, and can therefore hold any decimal value from 0 (00000000) to 255 (11111111).

1 Kilobyte  $\approx 1000$  bytes. In fact, 1KB = 1024 bytes =  $2^{10}$  bytes.

1Megabyte = 1024 kilobytes, 1 Gigabyte = 1024 megabytes.

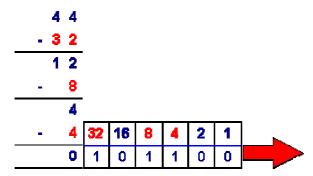

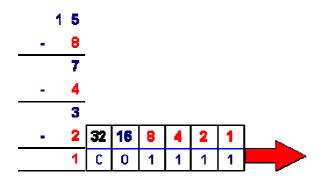

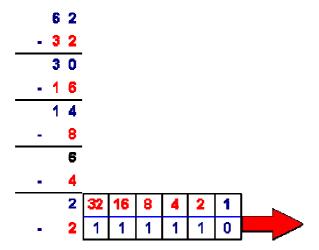

One way of converting a decimal (base 10) number to a binary (base 2) number is by divide the decimal number by 2:

```

600 / 2 = 300 \text{ rem. } 0 <-- LSB (least significant bit)

300 / 2 = 150 \text{ rem. } 0

150 / 2 = 75 \text{ rem. } 0

75 / 2 = 37 \text{ rem. } 1

37 / 2 = 18 \text{ rem. } 1

18 / 2 = 9 \text{ rem. } 0

9 / 2 = 4 \text{ rem. } 1

4 / 2 = 2 \text{ rem. } 0

2 / 2 = 1 \text{ rem. } 0

1 / 2 = 0 \text{ rem. } 1 <-- \text{MSB (most significant bit)}

1001011000

```

All of the remainders from the division are then arranged in reverse order, from MSB to LSB to form the correct binary sequence. 1001011000 in binary = 600 in decimal.

Computers perform repetitive, complex calculations; they cannot actually subtract binary numbers. To get around this problem, assume that, in sequence of bits, the first bit signifies whether the number is positive (0) or negative (1). The decimal number '+78' = 0100 1110, (where the first 0 bit shows that the number is positive), that is said to be the number's normal form. To find the number's 1's compliment, bits 2-8 are inverted, giving 0011 0001. To find the number's 2's compliment, 1 is added to this 1's compliment value, here giving 0011 0010. So, if the number was minus 78, its 2's compliment would be 1011 0010, where the first bit 1 defines the number as being negative. To subtract 20 from 45, we would have to think of that equation as being (+45) + (-20). By changing -20 from its natural from to its 2's compliment, we go from 1001 0100 to 1110 1011 to 1110 1100, using the process described above. When the binary equivalent of +45 (0010 1101) is added to the 2's compliment of -25, the following result is arrived at:

```

45 in normal form = 0010 1101

-20 in 2's compliment form = 1110 1100

+ ______

(1)0001 1001 = +25

```

By deleting the extra new bit at the start of the sequence,  $0001\ 1001$ , or +25 is correctly found to be the result.

### LOGIC GATES AND FUNCTIONS

### **Basic Logic Gates**

While each logical element or condition must always have a logic value of either "0" or "1", we also need to have ways to combine different logical signals or conditions to provide a logical result. For example, consider the logical statement:

### "If we move the switch on the wall up, the light will turn on."

At first glance, this seems to be a correct statement. However, if we look at a few other factors, we realize that there's more to it than this. In this example, a more complete statement would be:

"If we move the switch on the wall up and the light bulb is good and the power is on, the light will turn on." If we look at these two statements as logical expressions and use logical terminology, we can reduce the first statement to:

$$Light = Switch$$

This means nothing more than that the light will follow the action of the switch, so that when the switch is up/on/true/1 the light will also be on/true/1. Conversely, if the switch is down/off/false/0 the light will also be off/false/0. Looking at the second version of the statement, we have a slightly more complex expression:

Normally, we use symbols rather than words to designate the AND function that we're using to combine the separate variables of Switch, Bulb, and Power in this expression. The symbol normally used is a dot, which is the same symbol used for multiplication in some mathematical expressions. Using this symbol, our three-variable expression becomes:

When we deal with logical circuits (as in computers), we not only need to deal with logical functions; we also need some special symbols to denote these functions in a

logical diagram. There are three fundamental logical operations, from which all other functions, no matter how complex, can be derived. These functions are named *and*, *or*, *and not*. Each of these has a specific symbol and a clearly-defined behavior, as follows:

The AND Gate

The AND gate implements the AND function. With the gate shown above, both inputs must have logic 1 signals applied to them in order for the output to be logic 1. With either input at logic 0, the output will be held to logic 0. There is no limit to the number of inputs that may be applied to an AND function, however, for practical reasons, commercial AND gates are manufactured with 2, 3, or 4 inputs. A standard Integrated Circuit (IC) package contains 14 or 16 pins, for practical size and handling. A standard 14-pin package can contain four 2-input gates, three 3-input gates, or two 4-input gates, and still have room for two pins for power supply connections. The truth table for a two-input AND gate looks like

| A | В | A.B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

The OR Gate

The OR gate is sort of the reverse of the AND gate. The OR function, like its verbal counterpart, allows the output to be true (logic 1) if any one or more of its inputs are true. Verbally, we might say, "If it is raining OR if I turn on the sprinkler, the grass will be wet." Note that the grass will still be wet if the sprinkler is on and it is

also raining. This is correctly reflected by the basic OR function. In symbols, the OR function is designated with a plus sign (+). In logical diagrams, the symbol above designates the OR gate. As with the AND function, the OR function can have any number of inputs, however, practical commercial OR gates are limited to 2, 3, and 4 inputs, as with AND gates. The truth table for a two-input OR gate looks like

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

The NOT Gate, or Inverter

The inverter is a little different from AND and OR gates in that it always has exactly one input as well as one output. Whatever logical state is applied to the input, the opposite state will appear at the output. The NOT function is necessary in many applications and highly useful in others. A practical verbal application might be: **The door is NOT locked = you may enter**

The NOT function is denoted by a horizontal bar over the value to be inverted, as shown in the figure below. In the inverter symbol, the triangle actually denotes only an amplifier, which in digital terms means that it "cleans up" the signal but does not change its logical sense. It is the circle at the output which denotes the logical inversion. The circle could have been placed at the input instead, and the logical meaning would still be the same. The truth table for the NOT gate is shown below

| A | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

The logic gates shown above are used in various combinations to perform tasks of any level of complexity.

### **Derived Logic Functions and Gates**

Some combinations of basic functions have been given names and logic symbols of their own. The first is called NAND, and consists of an AND function followed by a NOT function. The second, as you might expect, is called NOR. This is an OR function followed by NOT. The third is a variation of the OR function, called the Exclusive-OR, or XOR function. Each of these derived functions has a specific logic symbol and behavior, which we can summarize as follows:

### The NAND Gate

The NAND gate implements the NAND function, which is exactly inverted from the AND function. Both inputs must have logic 1 signals applied to them in order for the output to be logic 0. With either input at logic 0, the output will be held to logic 1. The circle at the output of the NAND gate denotes the logical inversion, just as it did at the output of the inverter. The over-bar over both inputs shows that the AND function itself that is inverted, rather than each separate input. There is no limit to the number of inputs that may be applied to a NAND function, however, for practical reasons, commercial NAND gates are manufactured with 2, 3, or 4 inputs, to fit in a 14-pin or 16-pin package. The truth table for a two-input NAND gate looks like (— over A.B)

| A | В | A.B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

### The NOR Gate

The NOR gate is an OR gate with the output inverted. Where the OR gate allows the output to be true (logic 1) if any one or more of its inputs are true, the NOR gate inverts this and forces the output to logic 0 when any input is true.

In symbols, the NOR function is designated with a plus sign (+), with an over-bar over the entire expression to indicate the inversion. This is an OR gate with a circle to designate the inversion. The NOR function can have any number of inputs, but practical commercial NOR gates are mostly limited to 2, 3, and 4 inputs, as with other gates in this class, to fit in standard IC packages. The truth table for a two-input NOR gate looks like (— over A+B):

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

The Exclusive-OR, or XOR Gate

The Exclusive-OR, can be stated as, "Either A or B, but not both." The XOR gate produces logic 1 output only if its two inputs are different. If the inputs are the same, the output is logic 0. The XOR symbol is a variation on the standard OR symbol. It consists of a plus (+) sign with a circle around it. The logic symbol, as shown here, is a variation on the standard OR symbol. Unlike standard OR/NOR and AND/NAND functions, the XOR function always has exactly two inputs, and commercially manufactured XOR gates are the same. Four XOR gates fit in a

standard 14-pin IC package. The truth table for a two-input XOR gate looks like: (+ inside the circle of AOB)

| A | В | AOB |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

## The eXclusive-NOR (XNOR) gate

The exclusive-NOR or XNOR gate has two or more inputs. The output is equivalent to inverting the output from the exclusive-OR gate described above. Therefore an equivalent circuit would comprise an XOR gate, the output of which feeds into the input of a NOT gate. In general, an XNOR gate gives an output value of 1 when there are an **even** number of 1's on the inputs to the gate. The truth table for a 3-input XNOR gate below illustrates this point. The XNOR gate is drawn using the same symbol as the XOR gate with an invert circle on the output line.

The output from the XNOR gate is written as AOB which reads "A XNOR B".

The truth table for a two-input XNOR gate looks like

| A | В | AOB |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

37

# **SEQUENTIAL LOGIC**

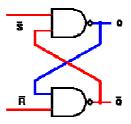

#### The Basic RS NAND Latch:

In order **for a logical circuit to "remember"** and retain its logical state even after the controlling input signal(s) have been removed, it is necessary for the circuit to include some form of **feedback**. We can use NAND or NOR gates, and using the extra input lines to control the circuit. The circuit shown below is a basic NAND latch with designated "S" and "R" for "Set" and "Reset" respectively. The **outputs** of any single-bit latch or memory are designated Q and Q'.

For the NAND latch circuit, both inputs should normally be at a logic1 level 1. Changing an input to a logic 0 level will force that output to logic 1. The same logic 1 will also be applied to the second input of the other NAND gate, allowing that output to fall to a logic 0 level. This in turn feeds back to the second input of the original gate, forcing its output to remain at logic1.

Applying another logic 0 input to the same gate will have no further effect on this circuit. However, applying logic 0 to the *other* gate will cause the same reaction in the other direction, thus changing the state of the latch circuit the other way.

It is <u>forbidden to have both inputs at a logic 0 level at the same time</u>. That state will force both outputs to a logic 1, overriding the feedback latching action. In this condition, whichever input goes to logic 1 first will lose control, while the other input (still at logic 0) controls the resulting state of the latch. If both inputs go to logic 1 simultaneously, the result is a "race" condition, and the final state of the latch cannot be determined ahead of time.

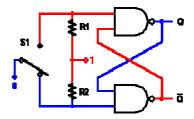

In this circuit, any mechanical switch added will experience a phenomenon called "contact bounce." Whenever you press the button or change the switch position, the physical contacts will flex a little, causing them to make and break several times before settling down. This is not noticed when turning on a light at home, but digital circuits are fast enough that they **do** notice this behavior. The solution is to use a pushbutton or switch, as shown in the figure below:

The unconnected input is held at a logic1 through its resistor, while the connected input is held at logic 0 by the direct connection through the switch.

When the button of the switch is pressed, the very first contact will cause the latch to change state, but additional bounces will have no further effect. This eliminates the contact bounce and sends a single, clean digital transition to the next circuit. One problem with the basic RS NAND latch is that the input levels need to be inverted, sitting idle at logic 1, in order for the circuit to work. It would be helpful if we had normal inputs which would idle at logic 0, and go to logic 1 only to control the latch. This can be done by placing inverters at the inputs. Another problem is how to control when the latch is allowed to change state, and when it is not. This is necessary if a group of latches and want to be sure they all change state (or not) at the same time. Both of these concerns can be easily addressed when using a Basic RS-NOR Latch.

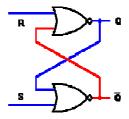

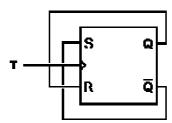

#### The Basic RS-NOR Latch:

The circuit shown below is a basic NOR latch. The inputs are generally designated "S" and "R" for "Set" and "Reset" respectively. **Because the NOR inputs must normally be logic 0 to avoid overriding the latching action, the inputs are not inverted in this circuit**. For the NOR latch circuit, **both inputs should normally be at**

**a logic 0** level. Changing an input to logic 1 level will force that output to logic 0. The same logic 0 will also be applied to the second input of the other NOR gate, allowing that output to raise to logic 1 level. This in turn feeds back to the second input of the original gate, forcing its output to remain at logic 0 even after removing external input.

Applying another logic1 input to the same gate will have no further effect on this circuit. However, applying logic 1 to the *other* gate will cause the same reaction in the other direction, thus changing the state of the latch circuit the other way. It is **forbidden** to have both inputs at a logic1 level at the same time. That state will force both outputs to logic 0, overriding the feedback latching action. In this condition, whichever input goes to logic 0 first will lose control, while the other input (still at logic 1) controls the resulting state of the latch. If both inputs go to logic 0 simultaneously, the result is a "race" condition, and the final state of the latch cannot be determined ahead of time. One problem with the basic RS NOR latch is that the input signals actively drive their respective outputs to a logic 0, rather than to a logic 1. Thus, the S input signal is applied to the gate that produces the Q' output, while the R input signal is applied to the gate that produces the Q output. The circuit works fine, but the input reversal is confusing.

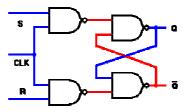

## The Clocked RS-NAND Latch:

By adding a pair of NAND gates to the input circuits of the RS latch, we accomplish two goals: normal rather than inverted inputs and a third input common to both gates which we can use to synchronize this circuit with others of its kind. The clocked RS NAND latch is shown below.

The clocked RS latch circuit is very similar in operation to the basic RS-NOR latch. The S and R inputs are normally at logic 0, and must be changed to logic 1 to change the state of the latch. However, with the third input, a new factor has been added. This input is typically designated C or CLK, because it is typically controlled by a clock circuit of some sort, which is used to synchronize several of these latch circuits with each other. The output can only change state while the CLK input is logic 1. When CLK is logic 0, the S and R inputs will have no effect.

The same rule about not activating both the S and R inputs simultaneously holds true: if both are logic 1 when the clock is also logic 1, the latching action is bypassed and both outputs will go to logic 1. The difference in this case is that if the CLK input drops to logic 0 first, there is no question or doubt -- a true race condition will exist, and we cannot tell which way the outputs will come to rest.

For correct operation, the selected R or S input should be brought to logic 1, and then the CLK input should be made logic 1 and then logic 0 again. Finally, the selected input should be returned to logic 0. The clocked RS latch solves some of the problems of basic RS latch circuit, and allows closer control of the latching action but does not offer a complete solution. A major problem remaining is that this latch circuit could easily experience a change in S and R input levels while the CLK input is still at logic 1 level. This allows the circuit to change state many times before the CLK input returns to logic 0. One way to solve this problem is by using The Edge-Triggered RS Flip-flop to make sure that the latch can only change its outputs at one instant of the clock cycle

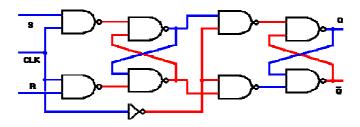

#### The Edge-Triggered RS Flip-flop:

To adjust the clocked RS latch for edge triggering, we must actually combine two identical clocked latch circuits, but have them operate on opposite halves of the clock signal. The resulting circuit is commonly called a *flip-flop*, because its

output can first flip one way and then flop back the other way. The clocked RS latch is also sometimes called a flip-flop, although it is more properly referred to as a latch circuit. The two-section flip-flop is also known as a *master-slave* flip-flop, because the input latch operates as the master section, while the output section is slaved to the master during half of each clock cycle. The edge-triggered RS NAND flip-flop is shown below.

The edge-triggered RS flip-flop consists of two identical RS latch circuits, as shown above. The inverter connected between the two CLK inputs ensures that the two sections will be enabled during opposite half-cycles of the clock signal. This is the key to the operation of this circuit.

If we start with the CLK input at logic 0, the S and R inputs are disconnected from the input (master) latch. Therefore, any changes in the input signals cannot affect the state of the final outputs. When the CLK signal goes to logic 1, the S and R inputs are able to control the state of the input latch, just as with the single RS latch circuit. At the same time, the inverted CLK signal applied to the output (slave) latch prevents the state of the input latch from having any effect here. Therefore, any changes in the R and S input signals are tracked by the input latch while CLK is at logic 1, but are not reflected at the Q and Q' outputs.

When CLK falls again to logic 0, the S and R inputs are again isolated from the input latch. At the same time, the inverted CLK signal now allows the current state of the input latch to reach the output latch. Therefore, the Q and Q' outputs can only change state when the CLK signal falls from a logic 1 to logic 0. This is known as the *falling edge* of the CLK signal; hence the designation *edge-triggered* flip-flop. There is still one problem left to solve: the possible race condition which may occur if both the S and

<u>R inputs are at logic 1 when CLK falls from logic 1 to logic 0.</u> The solution is to add some additional feedback from the slave latch to the master latch. The resulting circuit is called a *JK flip-flop*.

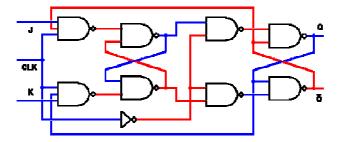

## The JK Flip-flop:

To prevent any possibility of a "race" condition occurring when both the S and R inputs are at logic 1 when the CLK input falls from logic 1 to logic 0, we must prevent one of those inputs from having an effect on the master latch in the circuit. At the same time, we still want the flip-flop to be able to change state on each falling edge of the CLK input, if the input logic signals call for this. Therefore, the S or R input to be disabled depends on the current state of the slave latch outputs.

If the Q output is logic 1 (the flip-flop is in the "Set" state), the S input can't make it any more set than it already is. Therefore, we can disable the S input without disabling the flip-flop under these conditions. In the same way, if the Q output is logic 0 (the flip-flop is reset), the R input can be disabled without causing any harm. If we can accomplish this, then we will solve the problem of the "race" condition.

The circuit below shows the solution. To the RS flip-flop we have added two new connections from the Q and Q' outputs back to the original input gates. We change the designations of the logic inputs and of the flip-flop itself to J (instead of S) and K (instead of R). The entire circuit is known as a *JK flip-flop*.

In most ways, the JK flip-flop behaves just like the RS flip-flop. The Q and Q' outputs will only change state on the falling edge of the CLK signal, and the J and K inputs will control the future output state pretty much as before. However, there are some important differences. Since one of the two logic inputs is always disabled according to

the output state of the overall flip-flop, the master latch cannot change state back and forth while the CLK input is at logic 1. Instead, the enabled input can change the state of the master latch *once*, after which this latch will not change again. This was not true of the RS flip-flop.

If both the J and K inputs are held at logic 1 and the CLK signal continues to change, the Q and Q' outputs will simply change state with each falling edge of the CLK signal. (The master latch circuit will change state with each *rising* edge of CLK.). Because the behavior of the JK flip-flop is completely predictable under all conditions, this is the preferred type of flip-flop for most logic circuit designs. The RS flip-flop is only used in applications where it can be guaranteed that both R and S cannot be logic 1 at the same time.

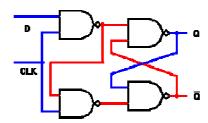

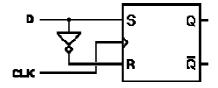

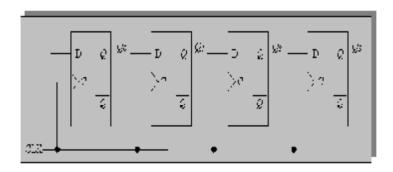

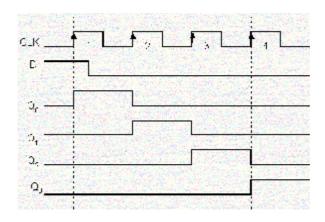

#### The D Latch (Data Latch):

One very useful variation on the RS latch circuit is the Data latch which is constructed by using the inverted S input as the R input signal. The single remaining input is designated "D" to distinguish its operation from other types of latches. It makes no difference that the R input signal is effectively clocked twice, since the CLK signal will either allow the signals to pass both gates or it will not.

In the D latch, when the CLK input is logic 1, the Q output will always reflect the logic level present at the D input, no matter how that changes. When the CLK input falls to logic 0, the last state of the D input is trapped and held in the latch, for use by whatever other circuits may need this signal. Because the single D input is also inverted to provide the signal to reset the latch, this latch circuit cannot experience a "race" condition caused by all inputs being at logic 1 simultaneously. Therefore the D latch can be safely used in any circuit.

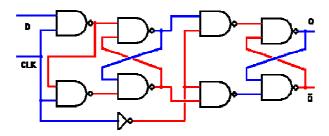

### The D Flip-flop:

Edge-triggered D flip-flop is derived from its RS ff after replacing R input with an inverted version of S input, which thereby becomes D. This is needed in the master latch section; the slave remains unchanged. In D flip-flop, when the clock input falls to logic 0 and the outputs can change state, the Q output always takes on the state of the D input at the moment of the clock edge. This was not true of the RS and JK flip-flops. The RS master section would repeatedly change states to match the input signals while the clock line is logic 1, and the Q output would reflect whichever input most recently received an active signal. The JK master section would receive and hold an input to tell it to change state, and never change that state until the next cycle of the clock.

### Flip-flop Symbols:

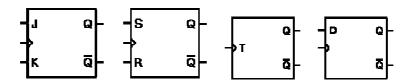

Placing all logic symbols in a diagram involving multiple flip-flops would rapidly generate so much clutter that the overall purpose of the diagram would be lost. To avoid this problem, we use the "black-box" approach. This is actually just one step further that the "black-box" approach we used in specifying logic gate symbols to represent specific clusters of electronic components — now we are using one symbol to represent a cluster of logic gates connected to perform a specific function. Some typical flip-flop symbols are shown below:

The symbols above are nearly identical — only the inputs vary. In each symbol the clock input is marked by small angle, rather than by letters CLK. That little angle marker actually provides two pieces of information, rather than one. First, of course, it marks the clocking input. Second, it specifies that these are edge-triggered flip-flops. The D latch shown uses a rounded marker for the clock input. This signifies that the circuit is controlled by the clock level, not the clock edge. If we change that rounded input to a sharp angle, it would indicate an edge-triggered master-slave D flip-flop.

#### **Converting Flip-flop Input Types:**

Sometimes it just happens that you need a particular type of flip-flop for a specific application, but all you have available is another type. This often happens with an application needing T flip-flops, since these are not generally available in commercial packages. Rather, it is necessary to re-wire an available type to perform as a T device. Converting an RS flip-flop involves simple feedback connections to ensure that the S and R inputs will always tell the flip-flop to change state at each clock pulse. Converting a D flip-flop to T operation is quite similar; the Q' output is connected back to the D input.

To convert an RS flip-flop to D operation, we need to add an inverter to supply the R input signal, as shown below:

# **Binary System**

Unlike analog circuit which contains signals that are constantly changing from one value to another, such as amplitude or frequency, digital circuits process signals that contain just two voltage levels or states, labeled **logic "0"** and **logic "1"**. These discrete voltage levels are commonly known as **BI**nary digi**TS** and are normally referred to as **BITS**. Because there are only two valid Boolean values for representing either logic "1" or logic "0", the **Binary Numbering** system is ideal for use in digital or electronic circuits and systems. The Binary Numbers system is a Base-2 system which follows the same rules in mathematics as the common decimal system meaning instead of powers of ten, for example 1, 10, 100, 1000 etc, binary uses powers of two, 1, 2, 4, 8, 16, 32 etc.

#### **Basic Concepts**

To understand binary numbers, begin by recalling elementary mathematics. In the decimal system, things are organized into columns:

```

H | T | O

9 | 2 | 4

```

Such that "H" is the hundreds column, "T" is the tens column, and "O" is the ones column. So the number "934" is 9-hundreds plus 2-tens plus 4-ones.

The ones column meant  $10^0$ , the tens column meant  $10^1$ , the hundreds column  $10^2$  and so on, such that

```

10^{2}|10^{1}|10^{0}

9 | 2 | 4

```

The number 924 is really  $\{(9*10^2)+(2*10^1)+(4*10^0)\}$ . The decimal system uses the digits 0-9 to represent numbers. If we wanted to put a larger number in column  $10^n$  (e.g., 10), we would have to multiply  $10*10^n$ , which would give  $10^{(n+1)}$ , and be carried a column to the left. For example, twelve would be  $12*10^0$ , or  $10^0(10+2)$ , or  $10^1+2*10^0$ . The binary system works under the exact same principles as the decimal system, only it operates in base 2 rather than base 10. In other words, instead of columns being  $10^2|10^1|10^0$ , they are  $2^2|2^1|2^0$ . Instead of using the digits 0-9, we only use 0-1 (again, if we used anything larger it would be like multiplying  $2*2^n$  and getting  $2^{n+1}$ , which would not fit in the  $2^n$  column. Therefore, it would shift you one column to the left. For example, "3" in binary cannot be put into one column. The first

column we fill is the right-most column, which is  $2^0$ , or 1. Since 3>1, we need to use an extra column to the left, and indicate it as "11" in binary  $(1*2^1) + (1*2^0)$ .

**Example:** What would the binary number 10, 111, 10101 and 11110 be in decimal notation? Remember:

## **Example:**

$$110100 = 1x2^{5} + 1x2^{4} + 0x2^{3} + 1x2^{2} + 0x2^{1} + 0x2^{0}$$

$$= 32 + 16 + 0 + 4 + 0 + 0$$

$$= 52$$

The same approach applies to non-integral numbers so, for example

$$110.101 = 1x2^{2} + 1x2^{1} + 0x2^{0} + 1x2^{-1} + 0x2^{-2} + 1x2^{-3}$$

$$= 4 + 2 + 0 + 0.5 + 0 + 0.125$$

$$= 6.625$$

## **Binary Addition**

Binary addition is completely straightforward and is done in the same way as standard decimal addition remembering that, in binary terms "one plus one equals zero carry one". This is also true for fractional binary numbers as illustrated below.

| Binary | Decimal | Binary  | Decimal | Binary    | Decimal |

|--------|---------|---------|---------|-----------|---------|

| 101    | 5       | 1001.1  | 9.5     | 110.1101  | 6.8125  |

| +110   | +6      | 1100.1  | +12.5   | +100.1010 | +4.6250 |

|        |         |         |         |           |         |

| 1011   | 11      | 10110.0 | 22.0    | 1011.0111 | 11.4375 |

Consider the addition of decimal numbers:

23

<u>+48</u>

We begin by adding 3+8=11. Since 11 is greater than 10, a one is put into the 10's column (carried), and a 1 is recorded in the one's column of the sum. Next, add  $\{(2+4)+1\}$  (the one is from the carry)=7, which is put in the 10's column of the sum. Thus, the answer is 71. Binary addition works on the same principle, but the numerals are different. Begin with one-bit binary addition:

1+1 carries us into the next column. In decimal form, 1+1=2 while in binary, any digit higher than 1 puts us a column to the left (as would 10 in decimal notations). The decimal number "2" is written in binary notation as "10" ( $1*2^1$ ) + ( $0*2^0$ ). Record the 0 in the ones column, and carry the 1 to the twos column to get an answer of "10." In our vertical notation,

```

1

<u>+1</u>

10

```

The process is the same for multiple-bit binary numbers:

```

1010

+1111

```

Step one:

Column  $2^0$ : 0+1=1.

Record the 1.

Temporary Result: 1; Carry: 0

Step two:

Column 2<sup>1</sup>: 1+1=10.

Record the 0, carry the 1.

Temporary Result: 01; Carry: 1

```

Step three:

```

Column  $2^2$ : 1+0=1 Add 1 from carry: 1+1=10.

Record the 0, carry the 1.

Temporary Result: 001; Carry: 1

Step four:

Column  $2^3$ : 1+1=10. Add 1 from carry: 10+1=11.

Record the 11.

Final result: 11001

Alternately:

11 (carry)

1010

+1111

11001

# Always remember

0+0=0

1+0=1

1+1=10

Try the following examples of binary addition:

# **Rules of Binary Addition**

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 0, and carry 1 to the next more significant bit

For example,

$$00011010 + 00001100 = 00100110$$

$$I I$$

$$0 0 0 1 1 0 1 0 = 26_{\text{(base 10)}}$$

$$+ 0 0 0 0 1 1 0 0 = 12_{\text{(base 10)}}$$

$$0 0 1 0 0 1 1 0 = 38_{\text{(base 10)}}$$

$$0 0 1 0 0 1 1 = 19_{\text{(base 10)}}$$

$$+ 0 0 1 1 1 1 1 0 = 62_{\text{(base 10)}}$$

$$0 1 0 1 0 0 0 1 = 81_{\text{(base 10)}}$$

Note: Rules of binary addition (without carries) are same as truths of the XOR gate.

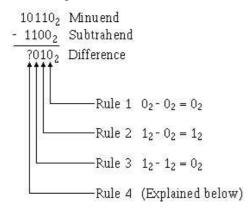

## **Binary Subtraction**

Binary subtraction usually takes place by *complementing* i.e. subtraction is via the addition of negative numbers. This technique requires the use of the so-called **ones** (1's) **complement** and **twos** (2's) **complement** of a binary number.

The 1's complement of a binary number is formed simply by complimenting each digit in turn. The 2's complement of a binary number is formed by adding 1 to the <u>least significant bit</u> of the 1's complement (**Note** in the case of fractional binary numbers this is <u>not</u> the same as adding 1 to the 1's complement number - see below).

| ] | Decimal | Binary    | 1's Complement | 2's Complement |

|---|---------|-----------|----------------|----------------|

|   | 5       | 00000101  | 11111010       | 11111011       |

| 2 | 27      | 00011011  | 11100100       | 11100101       |

| - | 76      | 01001100  | 10110011       | 10110100       |

|   | 4.625   | 0100.1010 | 1011.0101      | 1011.0110      |

Note that in order to correctly express the 1's complement and 2's complement binary numbers a fixed length format must be chosen (8-bit in the case above) and leading zeroes <u>must</u> be included when writing the original pure binary format number.