# EE101: Digital circuits (Part 4)

# M. B. Patil

mbpatil@ee.iitb.ac.in

www.ee.iitb.ac.in/~sequel

Department of Electrical Engineering Indian Institute of Technology Bombay

\* The digital circuits we have seen so far (gates, multiplexer, demultiplexer, encoders, decoders) are *combinatorial* in nature, i.e., the output(s) depends only on the *present* values of the inputs and *not* on their past values.

- \* The digital circuits we have seen so far (gates, multiplexer, demultiplexer, encoders, decoders) are *combinatorial* in nature, i.e., the output(s) depends only on the *present* values of the inputs and *not* on their past values.

- \* In sequential circuits, the "state" of the circuit is crucial in determining the output values. For a given input combination, a sequential circuit may produce different output values, depending on its previous state.

- \* The digital circuits we have seen so far (gates, multiplexer, demultiplexer, encoders, decoders) are *combinatorial* in nature, i.e., the output(s) depends only on the *present* values of the inputs and *not* on their past values.

- \* In sequential circuits, the "state" of the circuit is crucial in determining the output values. For a given input combination, a sequential circuit may produce different output values, depending on its previous state.

- \* In other words, a sequential circuit has a *memory* (of its past state) whereas a combinatorial circuit has no memory.

- \* The digital circuits we have seen so far (gates, multiplexer, demultiplexer, encoders, decoders) are *combinatorial* in nature, i.e., the output(s) depends only on the *present* values of the inputs and *not* on their past values.

- \* In sequential circuits, the "state" of the circuit is crucial in determining the output values. For a given input combination, a sequential circuit may produce different output values, depending on its previous state.

- \* In other words, a sequential circuit has a *memory* (of its past state) whereas a combinatorial circuit has no memory.

- \* Sequential circuits (together with combinatorial circuits) make it possible to build several useful applications, such as counters, registers, arithmetic/logic unit (ALU), all the way to microprocessors.

| Α | В | $X_1$ | $X_2$              |

|---|---|-------|--------------------|

|   |   |       |                    |

|   |   |       |                    |

|   |   |       |                    |

|   |   |       |                    |

|   | A | А В   | A B X <sub>1</sub> |

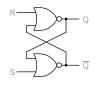

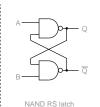

\* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

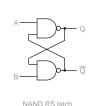

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A = 1, B = 0.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A = 1, B = 0.  $B = 0 \Rightarrow X_2 = 1 \Rightarrow X_1 = \overline{AX_2} = \overline{1 \cdot 1} = 0$ .

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

| A | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

|   |   |       |       |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs, X<sub>1</sub>, X<sub>2</sub>: outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs, X<sub>1</sub>, X<sub>2</sub>: outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs, X<sub>1</sub>, X<sub>2</sub>: outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs, X<sub>1</sub>, X<sub>2</sub>: outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.  $X_1 = \overline{A} X_2 = \overline{X_2}, \ X_2 = \overline{B} X_1 = \overline{X_1} \Rightarrow X_1 = \overline{X_2}$

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

|   |   |       |       |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.  $X_1 = \overline{AX_2} = \overline{X_2}, \ X_2 = \overline{BX_1} = \overline{X_1} \Rightarrow \overline{X_1 = \overline{X_2}}$

If  $X_1=1$ ,  $X_2=0$  previously, the circuit continues to "hold" that state. Similarly, if  $X_1=0$ ,  $X_2=1$  previously, the circuit continues to "hold" that state.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

| 1 | 1 | pre   | vious |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.  $X_1 = \overline{AX_2} = \overline{X_2}, X_2 = \overline{BX_1} = \overline{X_1} \Rightarrow \overline{X_1 = \overline{X_2}}$

If  $X_1=1$ ,  $X_2=0$  previously, the circuit continues to "hold" that state. Similarly, if  $X_1=0$ ,  $X_2=1$  previously, the circuit continues to "hold" that state.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

| 1 | 1 | pre   | vious |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.  $X_1 = \overline{AX_2} = \overline{X_2}, \ X_2 = \overline{BX_1} = \overline{X_1} \Rightarrow \overline{X_1 = \overline{X_2}}$

If  $X_1=1$ ,  $X_2=0$  previously, the circuit continues to "hold" that state. Similarly, if  $X_1=0$ ,  $X_2=1$  previously, the circuit continues to "hold" that state. The circuit has "latched in" the previous state.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

| 1 | 1 | pre   | vious |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.  $X_1 = \overline{AX_2} = \overline{X_2}, X_2 = \overline{BX_1} = \overline{X_1} \Rightarrow \overline{X_1 = \overline{X_2}}$

If  $X_1=1$ ,  $X_2=0$  previously, the circuit continues to "hold" that state. Similarly, if  $X_1=0$ ,  $X_2=1$  previously, the circuit continues to "hold" that state. The circuit has "latched in" the previous state.

\* For A = B = 0,  $X_1$  and  $X_2$  are both 1. This combination of A and B is *not* allowed for reasons that will become clear later.

| Α | В | $X_1$ | $X_2$ |

|---|---|-------|-------|

| 1 | 0 | 0     | 1     |

| 0 | 1 | 1     | 0     |

| 1 | 1 | pre   | vious |

| 0 | 0 | 1     | 1     |

|   |   |       |       |

- \* A, B: inputs,  $X_1$ ,  $X_2$ : outputs

- \* Consider A=1, B=0.  $B=0 \Rightarrow X_2=1 \Rightarrow X_1=\overline{AX_2}=\overline{1\cdot 1}=0$ . Overall, we have  $X_1=0$ ,  $X_2=1$ .

- \* Consider A = 0, B = 1. Show that  $X_1 = 1$ ,  $X_2 = 0$ .

- \* Consider A = B = 1.

$$X_1 = \overline{A X_2} = \overline{X_2}, \ X_2 = \overline{B X_1} = \overline{X_1} \Rightarrow X_1 = \overline{X_2}$$

If  $X_1=1$ ,  $X_2=0$  previously, the circuit continues to "hold" that state. Similarly, if  $X_1=0$ ,  $X_2=1$  previously, the circuit continues to "hold" that state. The circuit has "latched in" the previous state.

\* For A = B = 0,  $X_1$  and  $X_2$  are both 1. This combination of A and B is *not* allowed for reasons that will become clear later.

| Α | В | $X_1$ $X_2$ |  |

|---|---|-------------|--|

| 1 | 0 | 0 1         |  |

| 0 | 1 | 1 0         |  |

| 1 | 1 | previous    |  |

| 0 | 0 | invalid     |  |

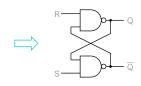

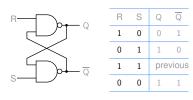

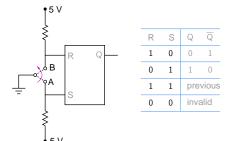

\* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

| Α | В | $X_1$    | $X_2$ |

|---|---|----------|-------|

| 1 | 0 | 0        | 1     |

| 0 | 1 | 1        | 0     |

| 1 | 1 | previous |       |

| 0 | 0 | inv      | alid  |

- \* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

- \* The combination A = 0, B = 1 serves to set  $X_1$  to 1 (*irrespective of* the previous state of the latch).

| Α | В | $X_1$    | $X_2$ |

|---|---|----------|-------|

| 1 | 0 | 0        | 1     |

| 0 | 1 | 1        | 0     |

| 1 | 1 | previous |       |

| 0 | 0 | inva     | alid  |

- \* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

- \* The combination A = 0, B = 1 serves to set  $X_1$  to 1 (irrespective of the previous state of the latch).

- \* In other words,

- A=1,  $B=0 \rightarrow latch gets reset to 0.$

- A = 0,  $B = 1 \rightarrow$  latch gets set to 1.

- \* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

- \* The combination A = 0, B = 1 serves to set  $X_1$  to 1 (irrespective of the previous state of the latch).

- \* In other words, A=1,  $B=0 \rightarrow$  latch gets reset to 0. A=0,  $B=1 \rightarrow$  latch gets set to 1.

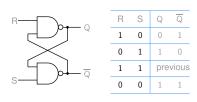

- \* The A input is therefore called the RESET (R) input, and B is called the SET (S) input of the latch.

|   | Α | В | $X_1$    | $X_2$ |

|---|---|---|----------|-------|

|   | 1 | 0 | 0        | 1     |

| ĺ | 0 | 1 | 1        | 0     |

| Ī | 1 | 1 | previous |       |

| ĺ | 0 | 0 | inva     | alid  |

- \* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

- \* The combination A = 0, B = 1 serves to set  $X_1$  to 1 (irrespective of the previous state of the latch).

- \* In other words, A=1,  $B=0 \rightarrow$  latch gets reset to 0. A=0,  $B=1 \rightarrow$  latch gets set to 1.

- \* The A input is therefore called the RESET (R) input, and B is called the SET (S) input of the latch.

- \*  $X_1$  is denoted by Q, and  $X_2$  (which is  $\overline{X_1}$  in all cases except for A=B=0) is denoted by  $\overline{Q}$ .

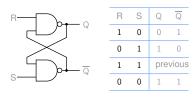

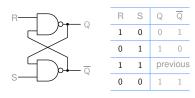

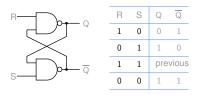

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

- \* The combination A=1, B=0 serves to reset  $X_1$  to 0 (irrespective of the previous state of the latch).

- \* The combination A = 0, B = 1 serves to set  $X_1$  to 1 (*irrespective of* the previous state of the latch).

- \* In other words, A=1,  $B=0 \rightarrow$  latch gets reset to 0. A=0,  $B=1 \rightarrow$  latch gets set to 1.

- \* The A input is therefore called the RESET (R) input, and B is called the SET (S) input of the latch.

- \*  $X_1$  is denoted by Q, and  $X_2$  (which is  $\overline{X_1}$  in all cases except for A=B=0) is denoted by  $\overline{Q}$ .

| R | S | Q   | Q     |

|---|---|-----|-------|

| 1 | 0 | 0   | 1     |

| 0 | 1 | 1   | 0     |

| 1 | 1 | pre | vious |

| 0 | 0 | inv | alid  |

| R | S | Q Q      |  |

|---|---|----------|--|

| 1 | 0 | 0 1      |  |

| 0 | 1 | 1 0      |  |

| 1 | 1 | previous |  |

| 0 | 0 | invalid  |  |

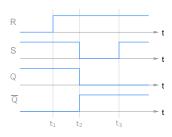

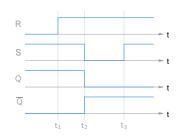

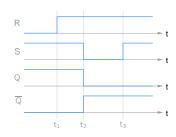

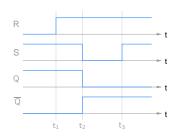

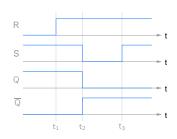

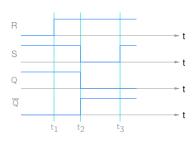

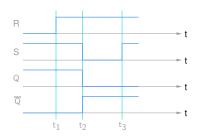

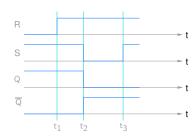

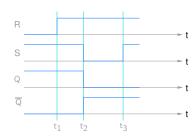

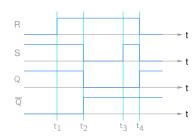

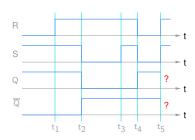

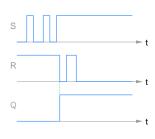

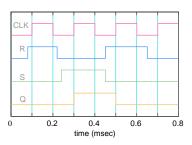

\* Up to  $t = t_1$ , R = 0,  $S = 1 \rightarrow Q = 1$ .

| R | S | $Q \overline{Q}$ |  |

|---|---|------------------|--|

| 1 | 0 | 0 1              |  |

| 0 | 1 | 1 0              |  |

| 1 | 1 | previous         |  |

| 0 | 0 | invalid          |  |

- \* Up to  $t = t_1$ , R = 0,  $S = 1 \rightarrow Q = 1$ .

- \* At  $t=t_1$ , R goes high  $\to R=S=1$ , and the latch holds its previous state  $\to$  no change at the output.

| R | S | Q   | Q     |

|---|---|-----|-------|

| 1 | 0 | 0   | 1     |

| 0 | 1 | 1   | 0     |

| 1 | 1 | pre | vious |

| 0 | 0 | inv | alid  |

- \* Up to  $t = t_1$ , R = 0,  $S = 1 \rightarrow Q = 1$ .

- \* At  $t=t_1$ , R goes high  $\to R=S=1$ , and the latch holds its previous state  $\to$  no change at the output.

- \* At  $t = t_2$ , S goes low  $\rightarrow R = 1$ ,  $S = 0 \rightarrow Q = 0$ .

| R S Q Q  1 0 0 1  0 1 1 0  1 1 previous |   |       |        |

|-----------------------------------------|---|-------|--------|

| 0 1 1 0                                 | R | S Q   | Q      |

|                                         | 1 | 0     | 1      |

| 1 1 previou                             | 0 | 1 1   | 0      |

|                                         | 1 | ı pre | evious |

| 0 0 invalid                             | 0 | ) inv | alid   |

- \* Up to  $t = t_1$ , R = 0,  $S = 1 \rightarrow Q = 1$ .

- \* At  $t=t_1$ , R goes high  $\to R=S=1$ , and the latch holds its previous state  $\to$  no change at the output.

- \* At  $t = t_2$ , S goes low  $\rightarrow R = 1$ ,  $S = 0 \rightarrow Q = 0$ .

- \* At  $t=t_3$ , S goes high  $\to R=S=1$ , and the latch holds its previous state  $\to$  no change at the output.

| R | S | Q        | Q |

|---|---|----------|---|

| 1 | 0 | 0        | 1 |

| 0 | 1 | 1        | 0 |

| 1 | 1 | previous |   |

| 0 | 0 | 1        | 1 |

|   |   |          |   |

\* Why not allow R = S = 0?

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* Why not allow R = S = 0?

- It makes  $Q=\overline{Q}=1$ , i.e., Q and  $\overline{Q}$  are not inverse of each other any more.

- More importantly, when R and S both become 1 simultaneously (starting from R=S=0), the final outputs Q and  $\overline{Q}$  cannot be uniquely determined. We could have Q=0,  $\overline{Q}=1$  or Q=1,  $\overline{Q}=0$ , depending on the delays associated with the two NAND gates.

- \* We surely don't want any question marks in digital electronics!

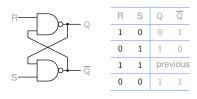

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 0 | 0 | pre  | vious |

| 1 | 1 | inva | alid  |

|   |   |      |       |

| R | S | Q        | Q    |

|---|---|----------|------|

| 1 | 0 | 0        | 1    |

| 0 | 1 | 1        | 0    |

| 0 | 0 | previous |      |

| 1 | 1 | inva     | alid |

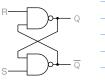

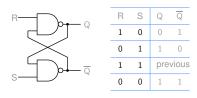

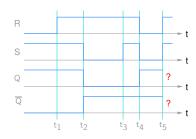

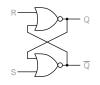

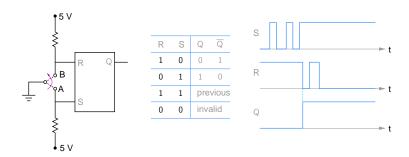

\* The NOR latch is similar to the NAND latch: When R=1, S=0, the latch gets reset to Q=0. When R=0, S=1, the latch gets set to Q=1.

| R | S | Q        | Q    |

|---|---|----------|------|

| 1 | 0 | 0        | 1    |

| 0 | 1 | 1        | 0    |

| 0 | 0 | previous |      |

| 1 | 1 | inva     | alid |

- \* The NOR latch is similar to the NAND latch: When R=1, S=0, the latch gets reset to Q=0. When R=0, S=1, the latch gets set to Q=1.

- \* For R = S = 0, the latch retains its previous state (i.e., the previous values of Q and  $\overline{Q}$ ).

| R | S | Q        | Q    |

|---|---|----------|------|

| 1 | 0 | 0        | 1    |

| 0 | 1 | 1        | 0    |

| 0 | 0 | previous |      |

| 1 | 1 | inva     | alid |

- \* The NOR latch is similar to the NAND latch: When R = 1, S = 0, the latch gets reset to Q = 0. When R = 0, S = 1, the latch gets set to Q = 1.

- \* For R = S = 0, the latch retains its previous state (i.e., the previous values of Q and  $\overline{Q}$ ).

- \* R = S = 1 is not allowed for reasons similar to those discussed in the context of the NAND latch.

# Comparison of NAND and NOR latches

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | prev | /ious |

| 0 | 0 | inva | lid   |

|   |   |      |       |

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 0 | 0 | pre  | vious |

| 1 | 1 | inva | alid  |

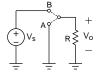

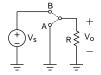

\* When the switch is thrown from A to B,  $V_o$  is expected to go from 0 V to  $V_s$  (say, 5 V).

\* When the switch is thrown from A to B,  $V_o$  is expected to go from 0 V to  $V_s$  (say, 5 V).

- \* When the switch is thrown from A to B,  $V_o$  is expected to go from 0 V to  $V_s$  (say, 5 V).

- \* However, mechanical switches suffer from "chatter" or "bouncing," i.e., the transition from A to B is not a single, clean one. As a result,  $V_o$  oscillates between 0 V and 5 V before settling to its final value (5 V).

- \* When the switch is thrown from A to B,  $V_o$  is expected to go from 0 V to  $V_s$  (say, 5 V).

- \* However, mechanical switches suffer from "chatter" or "bouncing," i.e., the transition from A to B is not a single, clean one. As a result,  $V_o$  oscillates between 0 V and 5 V before settling to its final value (5 V).

- \* When the switch is thrown from A to B,  $V_o$  is expected to go from 0 V to  $V_s$  (say, 5 V).

- \* However, mechanical switches suffer from "chatter" or "bouncing," i.e., the transition from A to B is not a single, clean one. As a result,  $V_o$  oscillates between 0 V and 5 V before settling to its final value (5 V).

- st In some applications, this chatter can cause malfunction ightarrow need a way to remove the chatter.

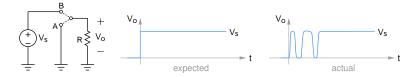

\* Because of the chatter, the S and R inputs may have multiple transitions when the switch is thrown from A to B.

- st Because of the chatter, the S and R inputs may have multiple transitions when the switch is thrown from A to B.

- \* However, for S = R = 1, the previous value of Q is retained, causing a *single* transition in Q, as desired.

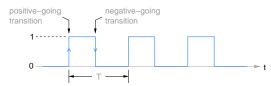

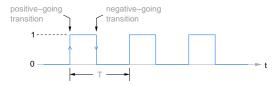

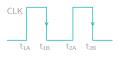

\* Complex digital circuits are generally designed for *synchronous* operation, i.e., transitions in the various signals are synchronised with the *clock*.

- \* Complex digital circuits are generally designed for *synchronous* operation, i.e., transitions in the various signals are synchronised with the *clock*.

- \* Synchronous circuits are easier to design and troubleshoot because the voltages at the nodes (both output nodes and internal nodes) can change only at specific times.

- \* Complex digital circuits are generally designed for *synchronous* operation, i.e., transitions in the various signals are synchronised with the *clock*.

- \* Synchronous circuits are easier to design and troubleshoot because the voltages at the nodes (both output nodes and internal nodes) can change only at specific times.

- \* A clock is a periodic signal, with a positive-going transition and a negative-going transition.

- \* Complex digital circuits are generally designed for *synchronous* operation, i.e., transitions in the various signals are synchronised with the *clock*.

- \* Synchronous circuits are easier to design and troubleshoot because the voltages at the nodes (both output nodes and internal nodes) can change only at specific times.

- \* A clock is a periodic signal, with a positive-going transition and a negative-going transition.

\* The clock frequency determines the overall speed of the circuit. For example, a processor that operates with a 1 GHz clock is 10 times faster than one that operates with a 100 MHz clock.

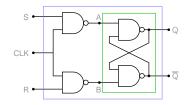

| CLK | R | S | Q    | Q     |

|-----|---|---|------|-------|

| 0   | Χ | Χ | pre  | vious |

| 1   | 1 | 0 | 0    | 1     |

| 1   | 0 | 1 | 1    | 0     |

| 1   | 0 | 0 | pre  | vious |

| 1   | 1 | 1 | inva | alid  |

NAND RS latch

| Α | В | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   | R | S | Q    | Q     |

|---|---|---|------|-------|

| 0 | Χ | Χ | pre  | vious |

| 1 | 1 | 0 | 0    | 1     |

| 1 | 0 | 1 | 1    | 0     |

| 1 | 0 | 0 | pre  | vious |

| 1 | 1 | 1 | inva | alid  |

| Α | В | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

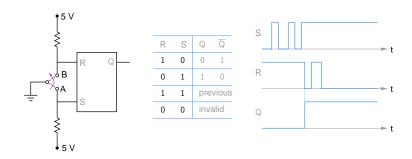

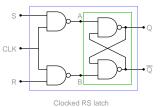

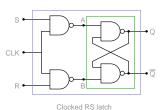

\* When clock is inactive (0), A = B = 1, and the latch holds the previous state.

| CLK | R | S | Q    | Q     |

|-----|---|---|------|-------|

| 0   | Χ | Χ | pre  | vious |

| 1   | 1 | 0 | 0    | 1     |

| 1   | 0 | 1 | 1    | 0     |

| 1   | 0 | 0 | pre  | vious |

| 1   | 1 | 1 | inva | alid  |

|     |   |   |      |       |

| Α | В | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

- \* When clock is inactive (0), A = B = 1, and the latch holds the previous state.

- \* When clock is active (1),  $A = \overline{S}$ ,  $B = \overline{R}$ . Using the truth table for the NAND RS latch (right), we can construct the truth table for the clocked RS latch.

| CLK | R | S | Q    | Q     |

|-----|---|---|------|-------|

| 0   | Χ | Χ | pre  | vious |

| 1   | 1 | 0 | 0    | 1     |

| 1   | 0 | 1 | 1    | 0     |

| 1   | 0 | 0 | pre  | vious |

| 1   | 1 | 1 | inva | alid  |

|     |   |   |      |       |

NAND RS latch

| А | В | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

- \* When clock is inactive (0), A = B = 1, and the latch holds the previous state.

- \* When clock is active (1),  $A = \overline{S}$ ,  $B = \overline{R}$ . Using the truth table for the NAND RS latch (right), we can construct the truth table for the clocked RS latch.

- \* Note that the above table is sensitive to the *level* of the clock (i.e., whether CLK is 0 or 1).

| CLK | R | S | Q    | Q     |

|-----|---|---|------|-------|

| 0   | Χ | Χ | pre  | vious |

| 1   | 1 | 0 | 0    | 1     |

| 1   | 0 | 1 | 1    | 0     |

| 1   | 0 | 0 | pre  | vious |

| 1   | 1 | 1 | inva | alid  |

(SEQUEL file: ee101\_rs\_1.sqproj)

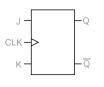

## Edge-triggered flip-flops

\* The clocked RS latch seen previously is *level-sensitive*, i.e., if the clock is active (CLK = 1), the flip-flop output is allowed to change, depending on the R and S inputs.

## Edge-triggered flip-flops

- \* The clocked RS latch seen previously is *level-sensitive*, i.e., if the clock is active (CLK = 1), the flip-flop output is allowed to change, depending on the R and S inputs.

- \* In an edge-sensitive flip-flop, the output can change only at the active clock edge (i.e., CLK transition from 0 to 1 or from 1 to 0).

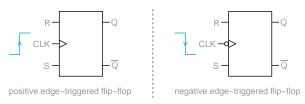

## Edge-triggered flip-flops

- \* The clocked RS latch seen previously is *level-sensitive*, i.e., if the clock is active (CLK = 1), the flip-flop output is allowed to change, depending on the R and S inputs.

- \* In an edge-sensitive flip-flop, the output can change only at the active clock edge (i.e., CLK transition from 0 to 1 or from 1 to 0).

- \* Edge-sensitive flip-flops are denoted by the following symbols:

| R | S | 0    | 0     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | prev | /ious |

| 0 | 0 | inva | ılid  |

Truth table for RS latch

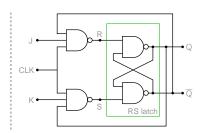

\* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

\* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J=K=0 \rightarrow R=S=1$ , RS latch holds previous Q, i.e.,  $Q_{n+1}=Q_n$ , where n denotes the  $n^{\text{th}}$  clock pulse (This notation will become clear shortly).

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

Truth table for RS latch

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

- J=0,  $K=1 \rightarrow R=1$ ,  $S=\overline{Q_n}$ .

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

- J = 0,  $K = 1 \to R = 1$ ,  $S = \overline{Q_n}$ . Case (i):  $Q_n = 0 \to S = 1$  (i.e., R = S = 1)  $\to Q_{n+1} = Q_n = 0$ .

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

- J = 0,  $K = 1 \to R = 1$ ,  $S = \overline{Q_n}$ . Case (i):  $Q_n = 0 \to S = 1$  (i.e., R = S = 1)  $\to Q_{n+1} = Q_n = 0$ . Case (ii):  $Q_n = 1 \to S = 0$  (i.e., R = 1, S = 0)  $\to Q_{n+1} = 0$ .

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

|     |   |   |                            |

|     |   |   |                            |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

- J=0,  $K=1 \rightarrow R=1$ ,  $S=\overline{Q_n}$ .

Case (i):

$$Q_n = 0 \rightarrow S = 1$$

(i.e.,  $R = S = 1$ )  $\rightarrow Q_{n+1} = Q_n = 0$ .

Case (ii):

$$Q_n = 1 \rightarrow S = 0$$

(i.e.,  $R = 1$ ,  $S = 0$ )  $\rightarrow Q_{n+1} = 0$ .

In either case,  $Q_{n+1} = 0 \rightarrow \text{For } J = 0$ , K = 1,  $Q_{n+1} = 0$ .

| R | S | Q       | Q     |

|---|---|---------|-------|

| 1 | 0 | 0       | 1     |

| 0 | 1 | 1       | 0     |

| 1 | 1 | pre     | vious |

| 0 | 0 | invalid |       |

|   |   |         |       |

Truth table for RS latch

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

|     |   |   |                            |

|     |   |   |                            |

Truth table for JK flip-flop

- \* When CLK = 0, we have R = S = 1, and the RS latch holds the previous Q. In other words, nothing happens as long as CLK = 0.

- \* When CLK = 1:

- $J = K = 0 \rightarrow R = S = 1$ , RS latch holds previous Q, i.e.,  $Q_{n+1} = Q_n$ , where n denotes the n<sup>th</sup> clock pulse (This notation will become clear shortly).

- J=0,  $K=1 \rightarrow R=1$ ,  $S=\overline{Q_n}$ .

Case (i):

$$Q_n = 0 \rightarrow S = 1$$

(i.e.,  $R = S = 1$ )  $\rightarrow Q_{n+1} = Q_n = 0$ .

Case (ii):

$$Q_n = 1 \rightarrow S = 0$$

(i.e.,  $R = 1$ ,  $S = 0$ )  $\rightarrow Q_{n+1} = 0$ .

In either case,  $Q_{n+1} = 0 \rightarrow \text{For } J = 0$ , K = 1,  $Q_{n+1} = 0$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

Truth table for RS latch

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

|     |   |   |                            |

|     |   |   |                            |

Truth table for JK flip-flop

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

Truth table for RS latch

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

|     |   |   |                            |

|     |   |   |                            |

Truth table for JK flip-flop

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{\overline{Q_n}}=Q_n$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

Truth table for RS latch

|   | CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|---|-----|---|---|----------------------------|

| Ī | 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

|   | 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| Ī | 1   | 0 | 1 | 0                          |

|   |     |   |   |                            |

|   |     |   |   |                            |

Truth table for JK flip-flop

\* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{\overline{Q_n}}=Q_n$ . Case (i):  $Q_n=0 \rightarrow R=0$  (i.e., R=0, S=1)  $\rightarrow Q_{n+1}=1$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

|     |   |   |                            |

|     |   |   |                            |

- Truth table for RS latch

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{\overline{Q_n}}=Q_n$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \rightarrow R = 1$  (i.e., R = 1, S = 1)  $\rightarrow Q_{n+1} = Q_n = 1$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

|     |   |   |                            |

|     |   |   |                            |

- Truth table for RS latch

- \* When CLK = 1:

- Consider

$$J=1$$

,  $K=0 \rightarrow S=1$ ,  $R=\overline{Q_n}=Q_n$ .

Case (i):

$$Q_n = 0 \rightarrow R = 0$$

(i.e.,  $R = 0$ ,  $S = 1$ )  $\rightarrow Q_{n+1} = 1$ .

Case (ii):

$$Q_n = 1 \rightarrow R = 1$$

(i.e.,  $R = 1$ ,  $S = 1$ )  $\rightarrow Q_{n+1} = Q_n = 1$ .

$$\rightarrow$$

For  $J = 1$ ,  $K = 0$ ,  $Q_{n+1} = 1$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

|     |   |   |                            |

- Truth table for RS latch

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{Q_n}=Q_n$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

Case (ii):

$$Q_n = 1 \rightarrow R = 1$$

(i.e.,  $R = 1$ ,  $S = 1$ )  $\rightarrow Q_{n+1} = Q_n = 1$ .

$$\rightarrow$$

For  $J = 1$ ,  $K = 0$ ,  $Q_{n+1} = 1$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

|     |   |   |                            |

Truth table for RS latch

Truth table for JK flip-flop

#### \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{Q_n}=Q_n$ .

Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

Case (ii):

$$Q_n = 1 \to R = 1$$

(i.e.,  $R = 1$ ,  $S = 1$ )  $\to Q_{n+1} = Q_n = 1$ .

→ For

$$J = 1$$

,  $K = 0$ ,  $Q_{n+1} = 1$ .

- Consider J=1,  $K=1 \rightarrow R=Q_n$ ,  $S=\overline{Q_n}$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

|     |   |   |                            |

- Truth table for RS latch

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{Q_n}=Q_n$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \rightarrow R = 1$  (i.e., R = 1, S = 1)  $\rightarrow Q_{n+1} = Q_n = 1$ .

- $\rightarrow$  For J = 1, K = 0,  $Q_{n+1} = 1$ .

- Consider J=1,  $K=1 \rightarrow R=Q_n$ ,  $S=\overline{Q_n}$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$ ,  $S = 1 \rightarrow Q_{n+1} = 1$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

|     |   |   |                            |

- Truth table for RS latch

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{\overline{Q_n}}=Q_n$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \to R = 1$  (i.e., R = 1, S = 1)  $\to Q_{n+1} = Q_n = 1$ .

- $\rightarrow$  For J = 1, K = 0,  $Q_{n+1} = 1$ .

- Consider J=1,  $K=1 \rightarrow R=Q_n$ ,  $S=\overline{Q_n}$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$ ,  $S = 1 \rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \to R = 1$ ,  $S = 0 \to Q_{n+1} = 0$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

| CLK | J | Κ | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

|     |   |   |                            |

Truth table for JK flip-flop

Truth table for RS latch

\* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{\overline{Q_n}}=Q_n$ .

Case (i):

$$Q_n = 0 \rightarrow R = 0$$

(i.e.,  $R = 0$ ,  $S = 1$ )  $\rightarrow Q_{n+1} = 1$ .

Case (ii):

$$Q_n = 1 \rightarrow R = 1$$

(i.e.,  $R = 1$ ,  $S = 1$ )  $\rightarrow Q_{n+1} = Q_n = 1$ .

$$\rightarrow$$

For  $J = 1$ ,  $K = 0$ ,  $Q_{n+1} = 1$ .

- Consider

$$J=1$$

,  $K=1 \rightarrow R=Q_n$ ,  $S=\overline{Q_n}$ .

Case (i):

$$Q_n = 0 \rightarrow R = 0$$

,  $S = 1 \rightarrow Q_{n+1} = 1$ .

Case (ii):

$$Q_n = 1 \to R = 1$$

,  $S = 0 \to Q_{n+1} = 0$ .

$$\rightarrow$$

For  $J=1$ ,  $K=1$ ,  $Q_{n+1}=\overline{Q_n}$ .

| R | S | Q    | Q     |

|---|---|------|-------|

| 1 | 0 | 0    | 1     |

| 0 | 1 | 1    | 0     |

| 1 | 1 | pre  | vious |

| 0 | 0 | inva | alid  |

|   |   |      |       |

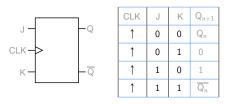

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

| 1   | 1 | 1 | toggles $(\overline{Q_n})$ |

Truth table for JK flip-flop

- Truth table for RS latch

- \* When CLK = 1:

- Consider J=1,  $K=0 \rightarrow S=1$ ,  $R=\overline{Q_n}=Q_n$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$  (i.e., R = 0, S = 1)  $\rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \rightarrow R = 1$  (i.e., R = 1, S = 1)  $\rightarrow Q_{n+1} = Q_n = 1$ .

- $\rightarrow$  For J = 1, K = 0,  $Q_{n+1} = 1$ .

- Consider J=1,  $K=1 \rightarrow R=Q_n$ ,  $S=\overline{Q_n}$ .

- Case (i):  $Q_n = 0 \rightarrow R = 0$ ,  $S = 1 \rightarrow Q_{n+1} = 1$ .

- Case (ii):  $Q_n = 1 \to R = 1$ ,  $S = 0 \to Q_{n+1} = 0$ .

- $\rightarrow$  For J=1, K=1,  $Q_{n+1}=\overline{Q_n}$ .

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

| 1   | 1 | 1 | toggles $(\overline{Q_n})$ |

|     |   |   |                            |

Truth table for JK flip-flop

Consider J = K = 1 and CLK = 1.

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

| 1   | 1 | 1 | toggles $(\overline{Q_n})$ |

|     |   |   |                            |

Truth table for JK flip-flop

Consider J = K = 1 and CLK = 1.

As long as  ${\sf CLK}=1$ , Q will keep toggling! (The frequency will depend on the delay values of the various gates).

| CLK | J | K | $Q\left(Q_{n+1}\right)$    |

|-----|---|---|----------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> ) |

| 1   | 0 | 0 | previous (Q <sub>n</sub> ) |

| 1   | 0 | 1 | 0                          |

| 1   | 1 | 0 | 1                          |

| 1   | 1 | 1 | toggles $(\overline{Q_n})$ |

|     |   |   |                            |

Truth table for JK flip-flop

Consider J = K = 1 and CLK = 1.

As long as  ${\sf CLK}=1$ , Q will keep toggling! (The frequency will depend on the delay values of the various gates).

When CLK changes from 1 to 0, the toggling will stop. However, the final value of  ${\it Q}$  is not known; it could be 0 or 1.

| CLK | J | K | $Q\left(Q_{n+1}\right)$             |

|-----|---|---|-------------------------------------|

| 0   | Χ | Χ | previous (Q <sub>n</sub> )          |

| 1   | 0 | 0 | previous (Q <sub>n</sub> )          |

| 1   | 0 | 1 | 0                                   |

| 1   | 1 | 0 | 1                                   |

| 1   | 1 | 1 | toggles $(\overline{\mathbb{Q}_n})$ |

|     |   |   |                                     |

Truth table for JK flip-flop

Consider J = K = 1 and CLK = 1.

As long as  ${\sf CLK}=1$ , Q will keep toggling! (The frequency will depend on the delay values of the various gates).

When CLK changes from 1 to 0, the toggling will stop. However, the final value of Q is not known; it could be 0 or 1.

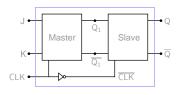

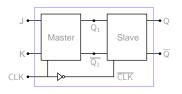

$\rightarrow$  Use the "Master-slave" configuration.

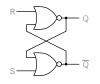

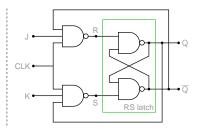

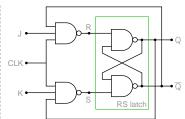

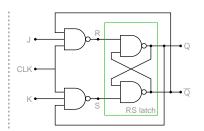

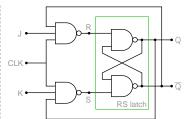

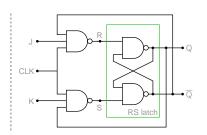

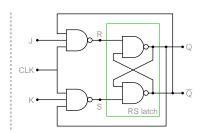

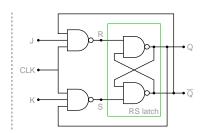

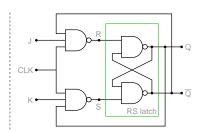

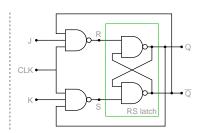

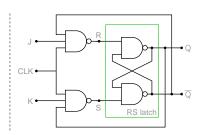

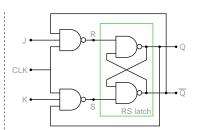

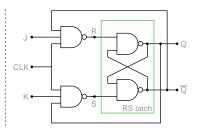

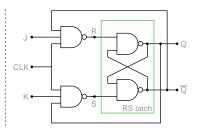

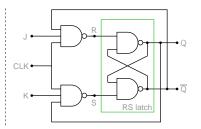

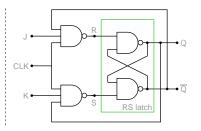

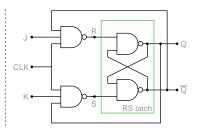

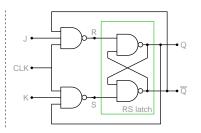

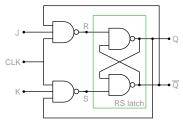

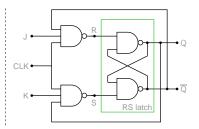

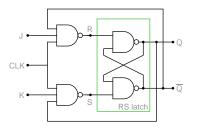

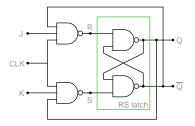

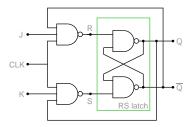

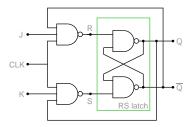

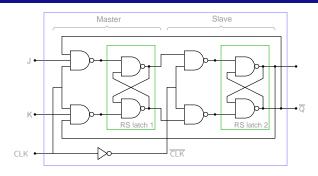

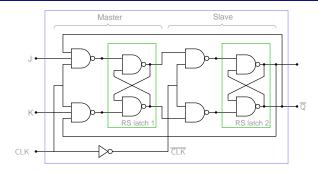

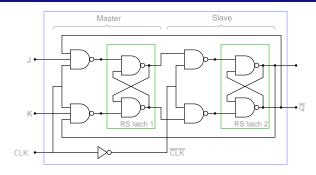

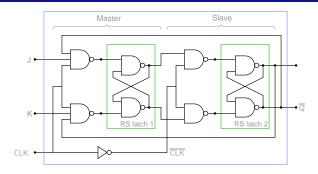

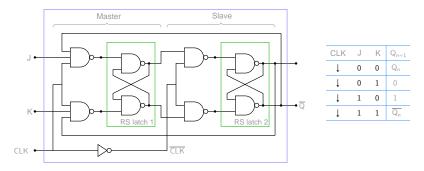

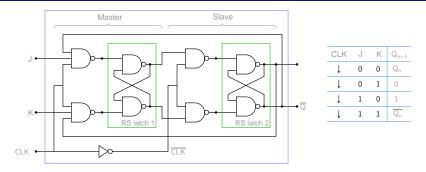

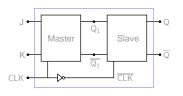

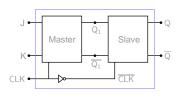

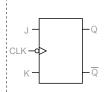

\* When CLK goes high, only the first latch is affected; the second latch retains its previous value (because  $\overline{\text{CLK}} = 0 \rightarrow R_2 = S_2 = 1$ ).

- \* When CLK goes high, only the first latch is affected; the second latch retains its previous value (because  $\overline{\text{CLK}} = 0 \to R_2 = S_2 = 1$ ).

- \* When CLK goes low, the output of the first latch  $(Q_1)$  is retained (since  $R_1 = S_1 = 1$ ), and  $Q_1$  can now affect Q.

- \* When CLK goes high, only the first latch is affected; the second latch retains its previous value (because  $\overline{\text{CLK}} = 0 \rightarrow R_2 = S_2 = 1$ ).

- \* When CLK goes low, the output of the first latch  $(Q_1)$  is retained (since  $R_1 = S_1 = 1$ ), and  $Q_1$  can now affect Q.

- \* In other words, the effect of any changes in J and K appears at the output Q only when CLK makes a transition from 1 to 0.

This is therefore a negative edge-triggered flip-flop.

- \* When CLK goes high, only the first latch is affected; the second latch retains its previous value (because  $\overline{\text{CLK}} = 0 \rightarrow R_2 = S_2 = 1$ ).

- \* When CLK goes low, the output of the first latch  $(Q_1)$  is retained (since  $R_1 = S_1 = 1$ ), and  $Q_1$  can now affect Q.

- \* In other words, the effect of any changes in J and K appears at the output Q only when CLK makes a transition from 1 to 0.

This is therefore a negative edge-triggered flip-flop.

- \* When CLK goes high, only the first latch is affected; the second latch retains its previous value (because  $\overline{\text{CLK}} = 0 \rightarrow R_2 = S_2 = 1$ ).

- \* When CLK goes low, the output of the first latch  $(Q_1)$  is retained (since  $R_1 = S_1 = 1$ ), and  $Q_1$  can now affect Q.

- \* In other words, the effect of any changes in J and K appears at the output Q only when CLK makes a transition from 1 to 0.

This is therefore a negative edge-triggered flip-flop.

- \* Note that, unlike the RS NAND latch which does not allow one of the combinations of R and S (viz., R=S=0), the JK flip-flop allows all four combinations.

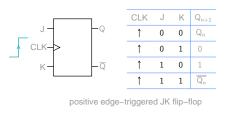

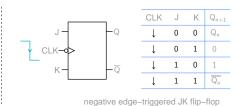

\* Both negative (e.g., 74101) and positive (e.g., 7470) edge-triggered JK flip-flops are available as ICs.

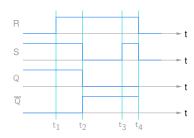

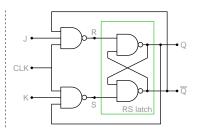

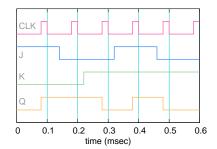

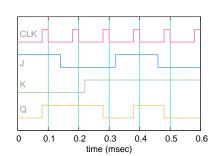

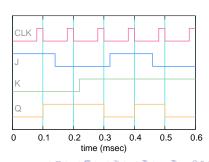

Consider a negative edge-triggered JK flip-flop.

\* As seen earlier, when CLK is high (i.e.,  $t_{1A} < t < t_{1B}$ , etc.), the input J and K determine the Master latch output  $Q_1$ . During this time, no change is visible at the flip-flop output Q.

- \* As seen earlier, when CLK is high (i.e.,  $t_{1A} < t < t_{1B}$ , etc.), the input J and K determine the Master latch output  $Q_1$ . During this time, no change is visible at the flip-flop output Q.

- When the clock goes low, the Slave flip-flop becomes active, making it possible for Q to change.

- \* As seen earlier, when CLK is high (i.e., t<sub>1A</sub> < t < t<sub>1B</sub>, etc.), the input J and K determine the Master latch output Q<sub>1</sub>.During this time, no change is visible at the flip-flop output Q.

- When the clock goes low, the Slave flip-flop becomes active, making it possible for Q to change.

- \* In short, although the flip-flop output Q can only change after the active edge,  $(t_{1B},\,t_{2B},\,$  etc.), the new Q value is determined by J and K values just before the active edge.

- \* As seen earlier, when CLK is high (i.e., t<sub>1A</sub> < t < t<sub>1B</sub>, etc.), the input J and K determine the Master latch output Q<sub>1</sub>.During this time, no change is visible at the flip-flop output Q.

- When the clock goes low, the Slave flip-flop becomes active, making it possible for Q to change.

- \* In short, although the flip-flop output Q can only change after the active edge,  $(t_{1B},\,t_{2B},\,$  etc.), the new Q value is determined by J and K values just before the active edge.

- This is a very important point!

| CLK | J | K | $Q_{n+1}$                   |

|-----|---|---|-----------------------------|

| 1   | 0 | 0 | Qn                          |

| 1   | 0 | 1 | 0                           |

| 1   | 1 | 0 | 1                           |

| 1   | 1 | 1 | $\overline{\mathbb{Q}_{n}}$ |

positive edge-triggered JK flip-flop

positive edge-triggered JK flip-flop

| CLK | J | K | $Q_{n+1}$                   |

|-----|---|---|-----------------------------|

| J   | 0 | 0 | Qn                          |

| 1   | 0 | 1 | 0                           |

| 1   | 1 | 0 | 1                           |

| ↓   | 1 | 1 | $\overline{\mathbb{Q}_{n}}$ |

negative edge-triggered JK flip-flop

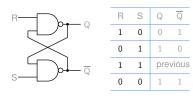

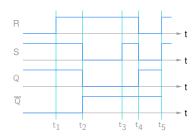

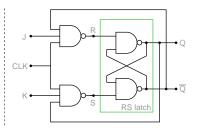

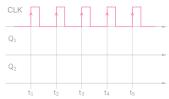

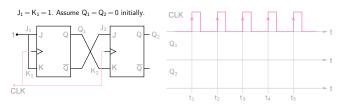

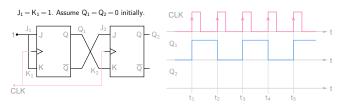

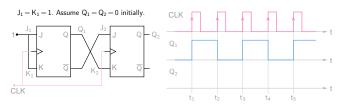

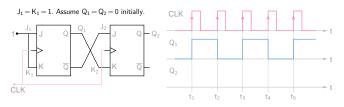

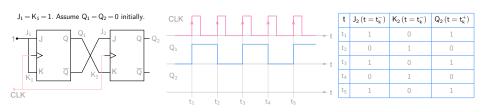

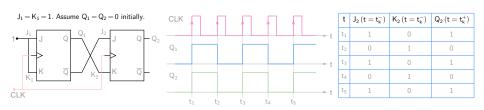

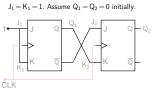

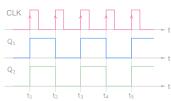

\* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

\* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \*  $J_2 = \overline{Q_1}$ ,  $K_2 = Q_1$ . We need to look at  $J_2$  and  $K_2$  values just before the active edge, to determine the next value of  $Q_2$ .

- \* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \*  $J_2 = \overline{Q_1}$ ,  $K_2 = Q_1$ . We need to look at  $J_2$  and  $K_2$  values *just before* the active edge, to determine the next value of  $Q_2$ .

- \* It is convenient to construct a table listing  $J_2$  and  $K_2$  to figure out the next  $Q_2$  value.

- \* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \* J<sub>2</sub> = Q

1, K<sub>2</sub> = Q

1. We need to look at J

2 and K

2 values just before the active edge, to determine the next value of Q

2.

- \* It is convenient to construct a table listing  $J_2$  and  $K_2$  to figure out the next  $Q_2$  value.

- \* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \* J<sub>2</sub> = Q

1, K<sub>2</sub> = Q

1. We need to look at J

2 and K

2 values just before the active edge, to determine the next value of Q

2.

- \* It is convenient to construct a table listing  $J_2$  and  $K_2$  to figure out the next  $Q_2$  value.

|   | t              | $J_{2}\left(t=t_{k}^{-}\right)$ | $K_{2}\left(t=t_{k}^{\scriptscriptstyle{-}}\right)$ | $Q_{2}\left(t=t_{k}^{+}\right)$ |

|---|----------------|---------------------------------|-----------------------------------------------------|---------------------------------|

| t | t <sub>1</sub> | 1                               | 0                                                   | 1                               |

|   | $t_2$          | 0                               | 1                                                   | 0                               |

| t | t <sub>3</sub> | 1                               | 0                                                   | 1                               |

|   | t <sub>4</sub> | 0                               | 1                                                   | 0                               |

| t | t <sub>5</sub> | 1                               | 0                                                   | 1                               |

|   |                |                                 |                                                     |                                 |

- \* Since  $J_1 = K_1 = 1$ ,  $Q_1$  toggles after every active clock edge.

- \* J<sub>2</sub> = Q<sub>1</sub>, K<sub>2</sub> = Q<sub>1</sub>. We need to look at J<sub>2</sub> and K<sub>2</sub> values just before the active edge, to determine the next value of Q<sub>2</sub>.

- \* It is convenient to construct a table listing  $J_2$  and  $K_2$  to figure out the next  $Q_2$  value.

- Note that the circuit is not doing much, apart from taxing our minds!

But hold on, some useful circuits will appear soon.